#### CS8491 COMPUTER ARCHITECTURE

#### II YEAR/4<sup>th</sup> SEMESTER, CSE

**Faculty Name:**

#### DEVI.P.P

#### Assistant Professor, CSE Department

Aalim Muhammed Salegh College of Engineering

#### **UNIT-I OVERVIEW & INSTRUCTIONS**

#### PART-A

#### 1. What are the five classic components of a computer?APR/MAY 2017

The five classic components of a computer are input, output, memory, datapath, and control, with the last two sometimes combined and called the processor.

#### 2. Define – Response Time

Response time is also called execution time. The total time required for the computer to complete a task, including disk accesses, memory accesses, I/O activities, operating system overhead, CPU execution time, and so on is called response time.

#### 3.Define - Throughput

Throughput or bandwidth is the total amount of work done in a given time.

#### 4. Write the CPU performance equation. APR/MAY 2018

The Classic CPU Performance Equation in terms of instruction count(the number of instructions executed by the program), CPI, and clock cycle time:

CPU time = Instruction count × CPI × Clock cycle time

or, since the clock rate is the inverse of clock cycle time:

$CPU time = \frac{Instruction count \times CPI}{Clock rate}$

5. If computer A runs a program in 10 seconds, and computer B runs the same program in 15 seconds, how much faster is A over B.10.

We know that A is *n* times as fast as B if

$\frac{\text{Performance}_{A}}{\text{Performance}_{B}} = \frac{\text{Execution time}_{B}}{\text{Execution time}_{A}} = n$

Thus the performance ratio is

$\frac{15}{10} = 1.5$

and A is therefore 1.5 times as fast as B.

#### 6. What are the basic components of performance?

The basic components of performance and how each is measured are:

| <b>Components of Performance</b> | Units of measure |

|----------------------------------|------------------|

| Components of refrontiance       | Units of measure |

|                                  |                  |

|                                  |                  |

| CPU execution time for a program  | Seconds for the program                        |

|-----------------------------------|------------------------------------------------|

| Instruction count                 | Instruction executed for the program           |

| Clock cycles per instruction(CPI) | Average number of clock cycles per instruction |

| Clock cycle time                  | Seconds per clock cycle                        |

### 7. Write the formula for CPU execution time for a program. [Dec 2015]

$\frac{\text{CPU execution time}}{\text{for a program}} = \frac{\text{CPU clock cycles}}{\text{for a program}} \times \text{Clock cycle time}$

Alternatively, because clock rate and clock cycle time are inverses,

$\frac{\text{CPU execution time}}{\text{for a program}} = \frac{\text{CPU clock cycles for a program}}{\text{Clock rate}}$

### 8. Write the formula for CPU clock cycles required for a program.

| CPU clock cycles =              | Instructions for a program | × per instruction |

|---------------------------------|----------------------------|-------------------|

| 사람이 가지 않는 말기에게, 안가가가 한 방법을 받았어? | 10                         | per motification  |

### 9. Define – MIPS

Million Instructions Per Second (MIPS) is a measurement of program execution speed based on the number of millions of instructions. MIPS is computed as:

MIPS is computed as:

$MIPS = \frac{Instruction \ count}{Execution \ time \times 10^6}$

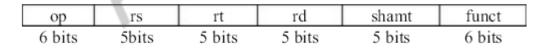

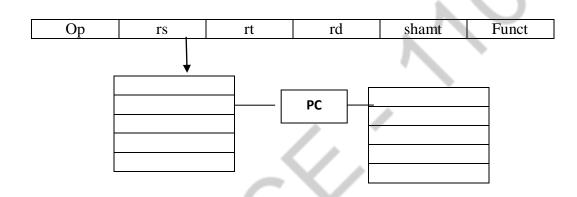

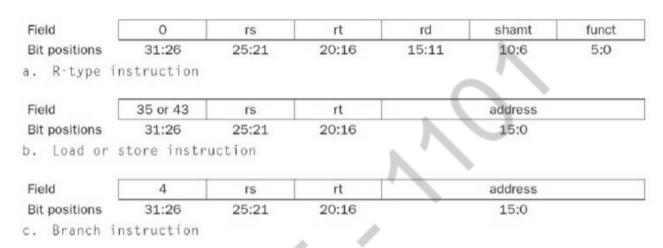

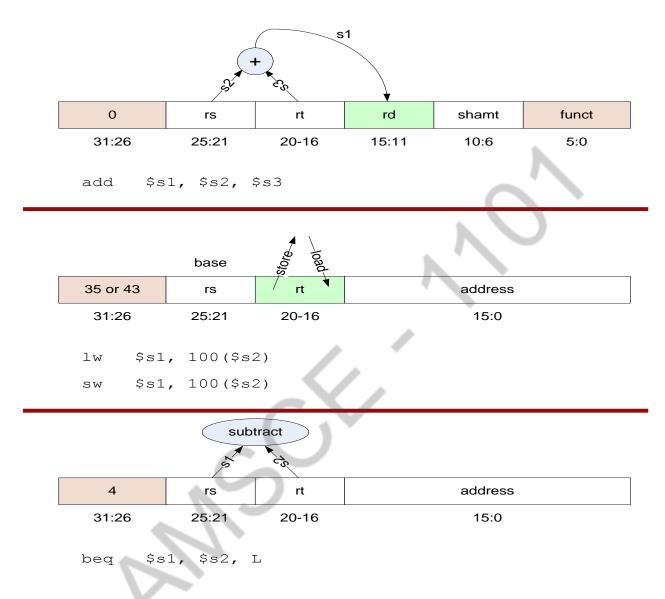

#### 10. What are the fields in an MIPS instruction?

MIPS fields are

Where,

op: Basic operation of the instruction, traditionally called the opcode.

rs: The first register source operand.

rt: The second register source operand.

rd: The register destination operand. It gets the result of the operation.

shamt: Shift amount.

funct: Function.

11. Write an example for immediate operand.

2

The quick add instruction with one constant operand is called add immediate or add i. To add 4 to register \$s3.

we just write

addi \$s3,\$s3,4 #\$s3 = \$s3 + 4

# 12. Define – Stored Program Concepts

Today's computers are built on two key principles:

- 1. Instructions are represented as numbers.

- 2. Programs are stored in memory to be read or written, just like data.

These principles lead to the stored-program concept. Treating instructions in the same way as data greatly simplifies both the memory hardware and the software of computer systems.

# 13. How to representing instruction in the computer system [May 2016]

- > Instructions are kept in computers as a series of high and low electric signals and represented as number.

- > Each piece of an instruction can be considered as an individual number .

- Placing these number side by side forms the instruction.

- R- format: register format

- I-format: intermediate format

- ➢ J − format: Jump format

# 14. Define – Addressing Modes

The different ways in which the operands of an instruction are specified are called as addressing modes.

The MIPS addressing modes are the following:

- Register addressing mode

- Immediate addressing mode.

- Base or displacement addressing mode

- Pc-relative addressing mode

- Pseudo- direct addressing mode

- In direct addressing mode

- Auto increment addressing mode

- 8.Auto decrement addressing mode

# 15.Define Register mode and Absolute Mode with examples.

# **Register mode:**

The operand is the contents of the processor register. The name (address) of the register is given in the instruction.

# Absolute Mode(Direct Mode):

> The operand is in new location. The address of this location is given explicitly in the instruction.

Eg: MOVE LOC,R2

The above instruction uses the register and absolute mode. The processor register is the temporary storage where the data in the register are accessed using register mode.

The absolute mode can represent global variables in the program.

| Mode          | Assembler Syntax | Addressing Function |

|---------------|------------------|---------------------|

| Register mode | Ri               | EA=Ri               |

| Absolute mode | LOC              | EA=LOC              |

Where EA-Effective Address

### 16.What is a Immediate addressing Mode?

The operand is given explicitly in the instruction. Eg: Move 200 immediate ,R0

▶ It places the value 200 in the register R0. The immediate mode used to specify the value of source operand.

In assembly language, the immediate subscript is not appropriate so # symbol is used. It can be re-written as

Move #200,R0

| Assembly Syntax: | Addressing Function |

|------------------|---------------------|

| Immediate #value | Operand =value      |

## 17.Define Indirect addressing Mode.(Nov/Dec2019), APR/MAY 2017

The effective address of the operand is the contents of a register .We denote the indirection by the name of the register or new address given in the instruction.

### **Fig: Indirect Mode**

Address of an operand (B) is stored into R1 register. If we want this operand, we can get it through register R1(indirection).

The register or new location that contains the address of an operand is called the pointer.

| Mode     | Assembler Syntax | Addressing Function |

|----------|------------------|---------------------|

| Indirect | Ri , LOC         | EA=[Ri] or EA=[LOC] |

### **18.Define Index addressing Mode.**

> The effective address of an operand is generated by adding a constant value to the contents of a register.

The constant value uses either special purpose or general purpose register. We indicate the index mode symbolically as,

$X(\mathbf{R}_i)$

Where  $\boldsymbol{X}-denotes the constant value contained in the instruction$

$R_i$  – It is the name of the register involved.

The Effective Address of the operand is,

EA=X + [Ri]

The index register R1 contains the address of a new location and the value of X defines an offset(also called a displacement).

# Eg: Add 20(R1), R2 (or) EA=>1000+20=1020

| Assembler Syntax | Addressing Function |  |

|------------------|---------------------|--|

|                  |                     |  |

| X(Ri)            | EA=[Ri]+X           |  |

| (Ri,Rj)          | EA=[Ri]+[Rj]        |  |

| X(Ri,Rj)         | EA=[Ri]+[Rj]+X      |  |

|                  | X(Ri)<br>(Ri,Rj)    |  |

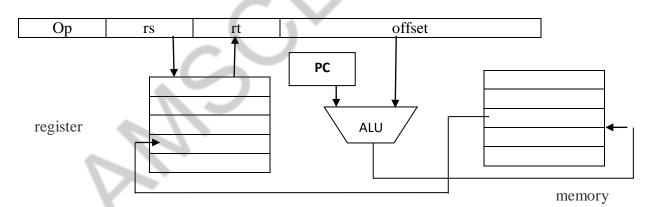

### 19. What is a Relative Addressing mode? [Dec 2015]

It is same as index mode. The difference is, instead of general purpose register, here we can use program counter(PC).

# **Relative Mode:**

- The Effective Address is determined by the Index mode using the PC in place of the general purpose register (gpr).

- This mode can be used to access the data operand. But its most common use is to specify the target address in branch instruction. Eg. Branch>0 Loop

- It causes the program execution to go to the branch target location. It is identified by the name loop if the branch condition is satisfied.

| Mode     | Assembler Syntax | Addressing Function |

|----------|------------------|---------------------|

|          |                  | r                   |

| Relative | X(PC)            | EA=[PC]+X           |

# 20.Define Auto-increment addressing mode. [May 2016]

- > The Effective Address of the operand is the contents of a register in the instruction.

- After accessing the operand, the contents of this register is automatically incremented to point to the next item in the list.

| Mode Assembler syntax |       | Addressing Function   |

|-----------------------|-------|-----------------------|

| Auto-increment        | (Ri)+ | EA=[Ri]; Increment Ri |

### 21.Define Auto-decrement addressing mode. [May 2016]

- > The Effective Address of the operand is the contents of a register in the instruction.

- After accessing the operand, the contents of this register is automatically decremented to point to the next item in the list.

| Mode           | Assembler Syntax | Addressing Function   |

|----------------|------------------|-----------------------|

| Auto-decrement | -(Ri)            | EA=[Ri]; Decrement Ri |

# PART-B

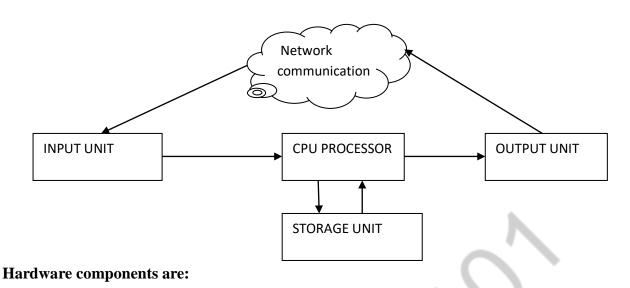

# **1.Explain in detail the various Components of a computer systems with neat** <u>diagram?</u>

# (MAY/ JUNE 2016, NOV/DEC 2015 , NOV/DEC 2014, APR/MAY 2018, APR/MAY 2019, NOV/DEC 2019)

> A computer in its simplest form is a fast electronic machine.

- It accepts digitize information from the user processes it according to a sequence of instruction and provides the processor information to the user.

- Components of computer system are hardware and software

1. Input unit 2. Output unit 3. Memory unit 4. Cpu

## 1. Input unit:

- > It is used for entering data and programs from user to computer system for processing.

- > Most commonly used input device are keyboard and mouse [Expalin].

## 2. Output unit:

- > It is used for displaying the results produced by the system after processing.

- > Most commonly used output devices are monitor, printer, plotter etc [Explain].

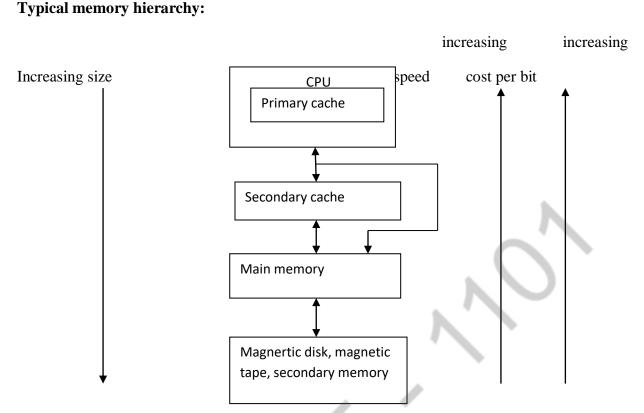

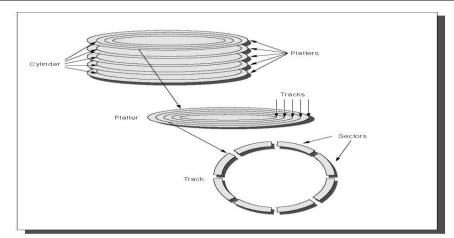

### 3. Memory unit:

- > It is used for storing data and instruction before and after processing.

- > It is divided into primary memory and secondary memory.[explain Ram,Rom]

## Primary memory (volatile main memory):

- ▶ It is fast semiconductor RAM.

- ➤ It loses instructions and data when power off.

- > It used to hold program while they are running.

### Secondary memory (non- volatile):

- ▶ It is magnetic tapes, magnetic disk are used for the storage of larger amount of data.

- ▶ A form of memory that retains data even in the absence of a power source.

- ➢ It is permanent storage device.

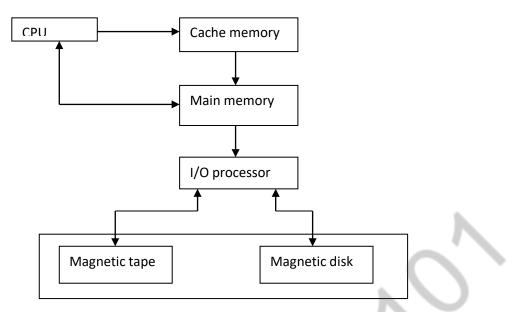

### 4. Central processing unit (CPU):

- Cpu is a brain of the system.

- Cpu takes data and instructions from the storage unit and makes all sorts of calculations based on the instructions gives, type of data provided.

- Cpu is dived into 2 sections namely:

# **1.ALU: arithmetic and logical unit.**

- > All arithmetic and logical operations are performed by the ALU.

- To perform these operations operands from the main memory are brought into internal registers of processor.

- ▶ After performing operation the result is either stored in the register or memory.

# 2. Control unit:

- > It co-ordinates and controls all the activities among the functional units.

- A basic function of control unit is to fetch the instructions stored in main memory, identify the operations and devices involved in it and accordingly generate control signals to execute the desired operations.

### Network communication:

Network have becomes so popular that they are the backbone of current computer systems.

## Networked computer have several major advantages:

- > *Communication*: Information is exchanged between computers at high speeds.

- Resource sharing: Rather than each computer having its own I/O devices, computers on the network can share I/O devices.

- > *Nonlocal access*: By connecting computers over long distances, users need not be near the computer they are using.

#### Software components: Software is a collection of progam Computer software is divided into two broad categories:

1. System software 2.Application software

### 1. System software:

- It is collection of programs which is needed in the creation, preparation and execution of other program.

- System software includes editor, assemblers, linker, loader, compilers, interpreters, debuggers and operating system

# 2. Application software:

- > Allows to perform specific task on a computer using capabilities of computer.

- > Application software to accomplish a task.

- > Different application software are needed to perform different tasks.

# **Operating system:**

- > OS Is a collection of routines that tells the computer what to do uner a variety of conditions.

- It is used to control the sharing of and interaction among various computer units as they execute application programs.

# 2. What is the need for Addressing in a computer system? Explain the different addressing modes with suitable examples? MAY/JUNE 2016, APR/MAY 2015, NOV/DEC 2015, APR/MAY 2017, APR/MAY 2018, <u>APR/MAY 2019</u>, NOV/DEC 2019

Addressing modes are the way of specifying an operand or memory address in an instruction.

The different ways in which the location of an operand is specified in an instruction are called address modes.

# Types of addressing modes:

• Register addressing mode

- Immediate addressing mode.

- Base or displacement addressing mode

- Pc-relative addressing mode

- Pseudo- direct addressing mode

- In direct addressing mode

- Auto increment addressing mode

- Auto decrement addressing mode

## **Register addressing mode:**

- ➤ Is the considered the simplest addressing mode.

- ➢ Because the operands are in register.

- > It allows the instructions to be executed much faster.

- > It is a form of direct addressing.

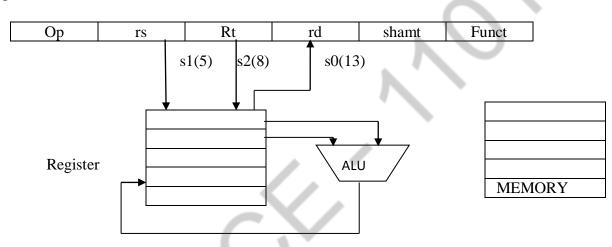

Example: add \$s0, Ss1, \$s2 where s1=5, s2=8

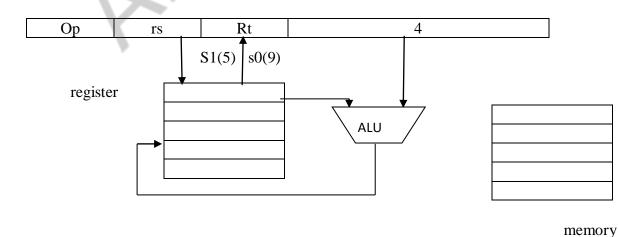

### **Immediate Addressing Mode:**

- > MIPS immediate addressing means that one operand is a constant within the instruction itself.

- > The advantage of using it is that there is no need to have extra memory access to fetch the operand.

- > But keep in mind that the operand is limited to 16 bits in size.

# **Example: addi \$s0, \$s1, 4** s1=5

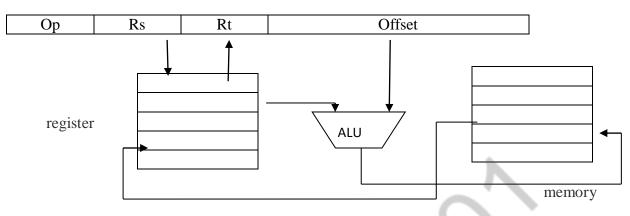

### Base or displacement addressing mode:

> Base address is a data or instruction memory location is specified as a signed offset from a register.

- ➢ It is also known as indirect addressing; a register act as a pointer to an operand located at the memory location whose address is in the register.

- > The address of the operand is the sum of the offset value and the base value.

- > The size of the operand is limited to 16 bits.

# Example: lw \$to,32 (\$s1)

# PC- relative addressing mode:

- > It is also known as program counter addressing.

- > It is a data or instruction memory location is specified as an offset relative to the incremented PC.

- > It is usually used in conditional branches.

- > Pc stores the address of next instruction to be fetched.

- It offset value can be an immediate value or an interpreted label value.

It implements position independent code.

# Example: beq \$s0, \$s1, label

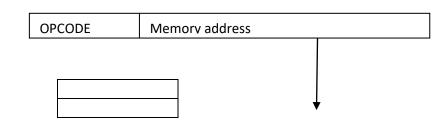

# Pseudo direct Addressing mode:

- $\succ$  It is the memory address which (mostly) embedded in the instructions.

- > It is specifically used for J-type instructions, j and jal.

- > The instruction format is 6 bits of opcode and 26 bits for the immediate value.

- > The effective address will always be a word aligned.

# Example: j label.

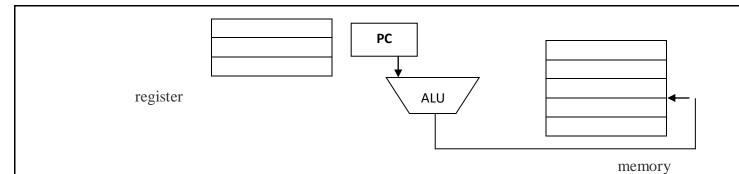

#### **Indirect Addressing Mode:**

It is also called register direct addressing mode

In this mode, the instruction contains the address of memory which refers the address of the operand.

Example: j \$s1 // s1= 4008 (address)

#### Auto increment addressing mode:

After accessing the operand, the content of this register are incremented to address the next location

### Example: Mov R0,(R2)+

#### Auto decrement addressing mode

The content of register specified in the instruction are first decremented ant then used an effective address of the operand

### Example : Mov – (R0),R2

# **<u>3. Discuss about the various techniques to represent instructions in the computer</u> <u>system?</u> APR/MAY 2015**

- Instructions are kept in computers as a series of high and low electric signals and represented as number.

- > Each piece of an instruction can be considered as an individual number .

- Placing these number side by side forms the instruction.

#### **Instruction format:**

A form of representation of an instruction composed of fields of binary numbers. In MIPS ISA instructions fall into 3 categories

### 1. R- format: register format

| 6  | 5  | 5 5 |    | 5     | 6     |

|----|----|-----|----|-------|-------|

| op | rs | Rt  | Rd | shamt | funct |

Where:

Op: basic operation of the instruction, traditionally called the opcode

Rs: the first register source operand. RS hold one of the argument of the operation

Rt: The second register source. Rt hold another arguments of the operation

Rd: The register destination operand. Rd stores the result of the operation.

Shamt: shift amount. Amount of bit to shift

Funct: function code. To specify the operation in addition to the opcode.

## Example: add \$t0, \$s1,\$s2 (R format)

|           | 6                              |            | 5     | 5                      |      | 5          | 5          | 6         |       |

|-----------|--------------------------------|------------|-------|------------------------|------|------------|------------|-----------|-------|

| R-        | ор                             | rs         |       | rt                     | ]    | Rd         | shamt      | funct     | forma |

|           |                                |            |       |                        |      |            |            |           |       |

|           | 0                              | 1          | 7     | 8                      |      | 25         | 0          | 32        |       |

| Decimal   |                                |            |       |                        |      |            |            |           |       |

| Binary    | 000000                         | ) 10       | 001   | 01000                  |      | 11001      | 00000      | 100000    |       |

| 2. I      | -format: in                    | termediate | -     | 5                      |      |            |            |           | 7     |

|           | 6                              |            | 5     | 5                      |      |            | 6          |           | _     |

|           | op                             |            | rs    | rt                     |      | Constant o | or address |           |       |

| lw \$t0,∶ | <b>32(\$s3)</b> ( <b>I</b> - 6 | - format)  |       | 5                      |      |            | 6          |           |       |

|           | ор                             | rs         |       | rt Constant or address |      |            |            |           |       |

|           |                                |            |       |                        |      |            |            |           |       |

| Decimal   |                                | 35         | 19    |                        | 8    |            | 32         |           |       |

| Bina      | iry                            | 00011      | 10011 | . 01                   | 1000 |            | 0000 0000  | 0010 0000 |       |

|           |                                |            |       |                        | 11   |            |            |           |       |

# 3. J – format: Jump format

| 6  | 36      |

|----|---------|

| op | Address |

### 4.Explain the various types of operations and operands supported by most of processors.

- > To command a computer hardware, you must speak in language.

- > The words of a computer language called instruction.

- > The collection of words is called instruction set.

- Machine instruction is in the form of binary codes.

- > Each instruction of cpu has specific information field which are required to execute it.

- Such information fields of instruction is called element of instruction.

### **Elements of instruction:**

- 1. Operation code: Specifies the operations to be performed.

- 2. Source/destination operand: Specifies the source/destination for the operand instruction.

- 3. Source operand address: Specified the instruction may require one or more source operands.

- 4. Destination operand address: The result stored in the destination operand

- 5. Next instruction address: To fetch the next instruction after completion of execution of current instruction

#### **Instruction types:**

- > Data processing Instruction :transfer the data between memory and register.

- > Arithmetic instruction performs arithmetic operation using numerical data.

- > The logical instruction performs logical operation on the bits of a word.

#### Data storage: memory instruction

The data has transfer between memory and register.

#### Data movement: data transfer instruction:

The data has transfer between cpu register and I/O devices

#### Control: test and branch instruction

Test instruction tests the value of a data word. Branch instruction depends on decision made. **Number of address:**

Computer may have instructions of different length containing varying number of address **Three address**: Three address instruction can be represent 2 source operands and 1 destination operand

Example: Add A,B,C

Two address: Two address instruction can be represent 1 source operand and another operand act as a

source as well as destination

Example: Add A,B

One address: One address instruction can be represent 1 source operand and accumulator act as a source

as well as destination

Example: Add AC, B

Zero address : In this all the operands are defined implicitly.

**Example:** AC  $\leftarrow$  AC

# 1. **Operations and operand**

### **Operations of computer hardware:**

- > Instructions step by step instructions in a top down fashion.

- > In MIPS processor (Advance Risk Machine (ARM)), the declaration is always done by the register.

- ➢ It support 32 bit register.

### MIPS (ARM) Assembly language:

| Category      | Instruction         | Example              |

|---------------|---------------------|----------------------|

|               | LOAD WORD           | Lw \$s1,20(\$s2)     |

|               | STORE WORD          | Sw \$s1, 20(\$s2)    |

| Data transfer |                     |                      |

| Arithmetic    | ADD                 | add \$s1, \$s2, \$s3 |

| instructions  | SUB                 | sub \$s1, \$s2, \$s3 |

|               | Add immediate       | addi \$s1, \$s2, 4   |

|               | Shift left logical  | sll \$s1, \$s2, 4    |

|               | Shift right logical | srl \$s1, \$s2, 4    |

| Conditional   | Branch on equal     | beq \$s1, \$s2, 5    |

| branch        | Branch on not equal | bne \$s1, \$s2, 5    |

| Unconditional | Jump                | j 2500               |

| branch        | Jump register       | jr \$ ra             |

### **Operands of the computer hardware:**

High level language, the operands of arithmetic instructions are restricted.

- Three types of operands:

- 1. 32 register operand

- 2.  $2^{30}$  memory words operand

- 3. Constant or immediate operand

### 32 register operand:

- Registers are primitives used in hardware design that are also visible to the programmers where the computer is completed.

- > The size of register in the MIPS (ARM) architecture is 32 bits.

| Register | 0      | 1    | 2-3       | 4-7       | 8-15      | 16-23     | 24-25     | 26-27     | 28   | 29   | 30   | 31   |  |

|----------|--------|------|-----------|-----------|-----------|-----------|-----------|-----------|------|------|------|------|--|

| Name     | \$Zero | \$at | \$v0-\$v1 | \$a0-\$a3 | \$t0-\$t7 | \$s0-\$s7 | \$t8-\$t9 | \$k0-\$k1 | \$gp | \$sp | \$fp | \$ra |  |

- at Reserved for assembler

- v0 v1 = value for results and expression evaluation

- a0 a3 = argument register

- t0 t7 = temporary register

- s0 s7 = saved register

- t8 t9 = more temporary register

- k0 k1 = reserved for operating system

- gp = global pointer

- sp = stack pointer

- fp = frame pointer

- ra = return address

#### Example: compiling a c assignment using register

### 2<sup>30</sup> memory word operand:

- Accessed only by data transfer instructions. MIPS (ARM) uses byte addresses.

- So sequential word addresses differ by 4byte.

- > Memory holds data, array, and spelled register.

| Memory [0] | Memory[4] | <br>Memory [ 4294967292] |

|------------|-----------|--------------------------|

#### Example: compiling an assignment when an operand is in memory

g = h + A[8]

| lw \$t0, 32 (\$s2) | [Effective address = base address + of | fset [offset = address *4 byte)]] |

|--------------------|----------------------------------------|-----------------------------------|

|                    | [ Effective address = $0 + 8 * 4$      | = 32]                             |

Add \$s0, \$s1, \$t0

Compiling using load and store: A[12] = h + A[8] LDR \$to,32(\$s1) STR \$t0,48(\$s1)

### **Constant or immediate operands:**

Program will use a constant in an operation.

In ARM arithmetic instructions have a constant as an operand.

#### **Example:**

a= b + 4

addi \$s0, \$s1, 4

### 5.Problem:

If a computer A runs a program in 10 second & B runs the same problem in 15 seconds how much faster is A than B?

$$\frac{\text{performance A}}{\text{performance B}} = \frac{\text{Execution time B}}{\text{Executiontime A}} = n$$

$$\frac{15}{10} = 1.5$$

A is therefore 1.5 times as fast as B

$\frac{\text{performance A}}{\text{performance B}} = 1.5$

$\frac{\text{performance A}}{1.5} = \text{performance B}$

6.Problems:

Computer A run a program in 12 seconds with a 3 GHz clock. We have to design a computer B such that it can run the same program within 9 seconds. Determine the clock rate for computer B. Assume that due to increase in clock cycle rate, CPU design of computer b is affected and it requires 1.2 times as many clock cycles as computer A for execution this program.

# Solution:

Clock rate  $A = 3 * 10^9$  cycles/sec CPU time A = 12 seconds CPU time B = 9 seconds

We have:

$$CPU time A = \frac{CPU clock cycles A}{Clock rate A}$$

$$12 \ seconds = \frac{\text{CPU clock cycles A}}{3 * 10^{-9} \text{ cycles/sec}}$$

CPU clock cycles A = 12 seconds \*  $3 * 10^9$  cycle /sec =  $36*10^9$  cycles

The cpu time for computer B can be given as

$$CPU time \ B = \frac{CPU \ clock \ cycles \ B}{Clock \ rate \ B}$$

$$CPU time \ B = \frac{1.2 * \ CPU \ clock \ cycles \ A}{CPU \ clock \ cycles \ A}$$

9 seconds =

$$\frac{1.2 * 36 * 10^9 \text{ cycles}}{\text{Clock rate B}}$$

clock rate  $B = \frac{1.2 * 36 * 10^9 \text{ cycles}}{9 \text{ second}} = 4.8 * 10^9 \text{ cycles} = 4.8 \text{ GHz}$

### 7.Problem:

The table shows the two code sequence with number of instructions of different instruction classes within each code sequence respectively. The instruction are classified as A,B and C according to the CPI as shown in table.

- (i) Determine which code sequence executes the most instructions.

- (ii) Determine which code sequence will execute quickly.

- (iii) Determine the CPI for each code sequence

| Code sequence | Instruction counts for each instruction class |   |   |  |  |  |

|---------------|-----------------------------------------------|---|---|--|--|--|

|               | А                                             | В | С |  |  |  |

| 1             | 4                                             | 2 | 4 |  |  |  |

| 2             | 8                                             | 2 | 2 |  |  |  |

Solution :

(i) Code sequence execution:

Code sequence 1 executes : 4+2+4 = 10 instructions Code sequence 2 executes : 8+2+2 = 12 instructions Therefore , code sequence 2 executes more instructions

#### (ii) CPU clock cycles required to executes these code sequences is given as

CPU clock cycles 1 = (4\*1) + (2\*2) + (4\*3) = 20 cycles CPU clock cycles 2 = (8\*1) + (2\*2) + (2\*3) = 18 cycles Code sequence 2 is faster than code sequence 1.

#### (iii) CPI for each code sequence

$CPI = \frac{CPU \text{ clock cycles}}{\text{Instruction count}}$

CPI  $1 = \frac{20}{10}$  = 2.0 CPI  $2 = \frac{18}{12}$  = 1.5

# 8. State the CPU performance equation and discuss the factors that affect performance APR/MAY 2017

Ans: Above three problems have to write.

#### **UNIT-II ARITHMETIC OPERATIONS**

#### 1. Add 6<sub>10</sub> to 7<sub>10</sub> in binary and Subtract 6<sub>10</sub> from 7<sub>10</sub> in binary.

Addition,

Subtraction directly,

|          | 0000         | 0000      | 0000 | 0000 | 0000 | 0000 | 0000 | 0111 <sub>two</sub> | - | 7 <sub>ten</sub>  |

|----------|--------------|-----------|------|------|------|------|------|---------------------|---|-------------------|

| -        | 0000         | 0000      | 0000 | 0000 | 0000 | 0000 | 0000 | 0110 <sub>two</sub> | = | 6 <sub>ten</sub>  |

| =        | 0000         | 0000      | 0000 | 0000 | 0000 | 0000 | 0000 | 0001 <sub>two</sub> | - | $1_{ten}$         |

| Or via t | wo's compler | ment of - | 6,   |      |      |      |      |                     |   |                   |

|          | 0000         | 0000      | 0000 | 0000 | 0000 | 0000 | 0000 | 0111 <sub>two</sub> | = | 7 <sub>ten</sub>  |

| +        | 1111         | 1111      | 1111 | 1111 | 1111 | 1111 | 1111 | $1010_{two}$        | = | -6 <sub>ten</sub> |

| -        | 0000         | 0000      | 0000 | 0000 | 0000 | 0000 | 0000 | 0001 <sub>two</sub> | - | 1 <sub>ten</sub>  |

#### 2. What are the floating point instructions in MIPS?

MIPS supports the IEEE 754 single precision and double precision formats with these instructions:

- Floating-point addition

- Floating-point subtraction

- Floating-point multiplication

- Floating-point division

- Floating-point comparison

### Floating-point branch

### 3. Define Guard and Round

Guard is the first of two extra bits kept on the right during intermediate calculations of floating point numbers. It is used to improve rounding accuracy.

Round is a method to make the intermediate floating-point result fit the floating-point format; the goal is typically to find the nearest number that can be represented in the format. IEEE 754, therefore, always keeps two extra bits on the right during intermediate additions, called guard and round, respectively.

### 4. Define ULP

Units in the Last Place is defined as the number of bits in error in the least significant bits of the significant between the actual number and the number that can be represented.

## 5. What is meant by sub-word parallelism? [May 2015/May 2016], APR/MAY 2017

Given that the parallelism occurs within a wide word, the extensions are classified as sub-word parallelism. It is also classified under the more general name of data level parallelism. They have been also called vector or SIMD, for single instruction, multiple data. The rising popularity of multimedia applications led to arithmetic instructions that support narrower operations that can easily operate in parallel.

For example, ARM added more than 100 instructions in the NEON multimedia instruction extension to support sub-word parallelism, which can be used either withARMv7 or ARMv8.

### 6. What is meant by sticky bit?

Sticky bit is a bit used in rounding in addition to guard and round that is set when ever there are nonzero bits to the right of the round bit. This sticky bit allows the computer to see the difference between 0.50 ... 00 ten and .... 01 ten when rounding

# 7. What are the steps in the floating-point addition? APR/MAY 2017

The steps in the floating-point addition are

- 1. Align the decimal point of the number that has the smaller exponent.

- 2. Addition of the significands.

- 3. Normalize the sum.

4. Round the result.

# 8. Write the IEEE 754 floating point format.

The IEEE 754 standard floating point representation is almost always an approximation of the real number

$(-1)^{s} \times (1 + \text{Fraction}) \times 2^{(\text{Exponent} - \text{Bias})}$

# 9.Write the overflow conditions for addition and subtraction [May 2015/Dec 2015]

| Operation | Operand A | Operand B | Result Indicating overflow |

|-----------|-----------|-----------|----------------------------|

| A+B       | $\geq 0$  | $\geq 0$  | <0                         |

| A+B       | <0        | <0        | $\geq 0$                   |

| A-B       | $\geq 0$  | <0        | <0                         |

| A-B       | <0        | $\geq 0$  | $\geq 0$                   |

### 10. Multiply 1000<sub>10</sub> \* 1001<sub>10</sub>.

| Multiplicand |          | $1000_{ten}$ |

|--------------|----------|--------------|

| Multiplier   | $\times$ | 1001ten      |

|              |          | 1000         |

|              |          | 0000         |

|              |          | 0000         |

|              |          | 1000         |

| Product      |          | 1001000ten   |

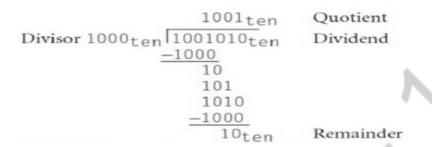

### 11. Divide 1,001,010 ten by 1000 ten

## 12. Define Little Endian arrangement? [Dec 2014]

When lower byte addresses are used for the less significant bytes (rightmost bytes) of the word.

Draw the diagram in notes

### 13.Define ALU [May 2016]

ALU stands for Arithmetic Logic Unit, ALU is responsible for performing arithmetic operations such as add, subtract, division and multiplication and logical operation such as AND, OR, Inverting etc.

Arithmetic operation to be performed is based on data type.

### Two basic data types:

- 1. Fixed point numbers

- 2. Floating point numbers

#### 14.State the representation of double precision of floating point number. [Dec 2015]

> The IEEE-754 double precision occupies a two 32 bit words.

| 63 | 62 |    | 52 51 |   | 0 |

|----|----|----|-------|---|---|

|    | ~  |    |       |   |   |

|    | S  | E' |       | Μ |   |

S : sign of number. 0- signifies +ve, 1- signifies -ve

- E': 11 bit signed exponent in excess-1023 representation.

- M: 52 bit mantissa fraction

# 15.what are overflow and underflow condition [Dec 2015]

# **Overflow:**

- > A situation in which a positive exponent becomes too large to fit in the exponent field.

- > In single precision , if the number requires an exponent greater than +127

- In double precision, if the number requires an exponent greater than +1023 underflow:

- A situation in which a negative exponent becomes too large to fit in the exponent field.

- ➢ In single precision , if the number requires an exponent less than -126

- > In double precision , if the number requires an exponent less than -1022

# 16. State the principle of operation of a carry look-ahead adder.

The input carry needed by a stage is directly computed from carry signals obtained from all the preceding stages i-1,i-2,....0, rather than waiting for normal carries to supply slowly from stage to stage. An adder that uses this principle is called carry look-ahead adder.

# 17.What are the main features of Booth's algorithm? NOV/DEC 2019

- > It handles both positive and negative multipliers uniformly.

- It achieves some efficiency in the number of addition required when the multiplier has a few large blocks of 1s.

# 18. How can we speed up the multiplication process?

There are two techniques to speed up the multiplication process:

- The first technique guarantees that the maximum number of summands that must be added is n/2 for n-bit operands.

- $\circ$   $\,$  The second technique reduces the time needed to add the summands.

# 19. What is bit pair recoding? Give an example.

- Bit pair recoding halves the maximum number of summands. Group the Booth-recoded multiplier bits in pairs and observe the following:

- The pair (+1 -1) is equivalent to the pair (0 +1). That is instead of adding -1 times the multiplicand m at shift position i to +1 ( M at position i+1, the same result is obtained by adding +1 ( M at position i. Eg: 11010 Bit Pair recoding value is 0 -1 -2

# 20. What is the advantage of using Booth algorithm?

▶ It handles both positive and negative multiplier uniformly.

- > It achieves efficiency in the number of additions required when the multiplier has a few large blocks of 1's.

- > The speed gained by skipping 1's depends on the data.

# 21.Write the algorithm for restoring division.

Do the following for n times:

- > Shift A and Q left one binary position.

- Subtract M and A and place the answer back in A.

- > If the sign of A is 1, set q0 to 0 and add M back to A. Where A- Accumulator, M- Divisor, Q- Dividend.

# 22.Write the algorithm for non restoring division.

Do the following for n times: Step 1: Do the following for n times:

- If the sign of A is 0, shift A and Q left one bit position and subtract M from A; otherwise, shift A and Q left and add M to A.

- > Now, if the sign of A is 0, set q0 to 1; otherwise, set q0 to 0.

Step 2: if the sign of A is 1, add M to A.

# 23. When can you say that a number is normalized?

When the decimal point is placed to the right of the first (nonzero) significant digit, the number is said to be normalized.

# 24. Explain about the special values in floating point numbers.

The end values 0 to 255 of the excess-127 exponent E are used to represent special values such as: When E=0 and the mantissa fraction M is zero the value exact 0 is represented. When E=255 and M=0, the value is represented.

When E=0 and M=0, denormal values are represented.

When E= 2555 and M = 0, the value represented is called Not a number.

# 25.What is the purpose of guard bits used in floating point arithmetic

Although the mantissa of initial operands are limited to 24 bits, it is important to retain extra bits, called as guard bits.

# 26.What are the ways to truncate the guard bits?

There are several ways to truncate the guard bits:

- 1) Chopping

- 2) Von Neumann rounding

- 3) Rounding

**27.Define carry save addition(CSA) process.** Instead of letting the carries ripple along the rows, they can be saved and introduced into the next roe at the correct weighted position. Delay in CSA is less than delay through the ripple carry adder.

# 28.What are generate and propagate function?

The generate function is given by Gi=xiyi and

The propagate function is given as

Pi=xi+yi.

# 29. What are the difficulties faced when we use floating point arithmetic?

Mantissa overflow: The addition of two mantissas of the same sign may result in a carryout of the most significant bit

Mantissa underflow: In the process of aligning mantissas ,digits may flow off the right end of the mantissa.

**Exponent overflow**: Exponent overflow occurs when a positive exponent exceeds the maximum possible value.

Exponent underflow: It occurs when a negative exponent exceeds the maximum possible exponent value.

# PART-B

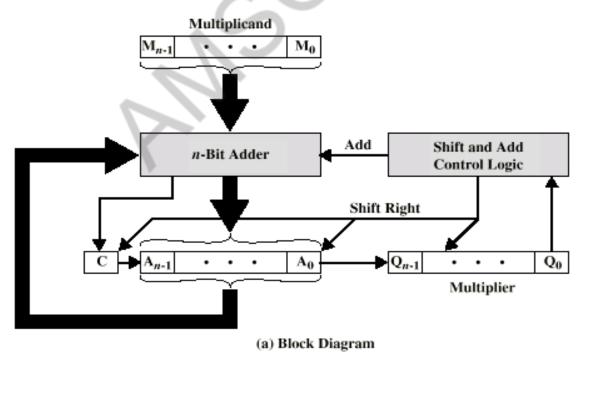

# **1. Explain in detail about the Multiplication algorithm with suitable example and** <u>diagram?</u> [Dec 2014/May 2015/Dec 2015/May 2016/ APR/MAY 2017/ APR/MAY 2018/MAY 2019]

# (i)Hardware implementation of unsigned binary multiplication:

- > The implementation of manual multiplication approach.

- > It consists of n-bit binary adder, shift and add control logic and four register A, B, C and Q.

Multiplier and multiplicand are loaded into Q and B register, respectively C are initially set to 0.

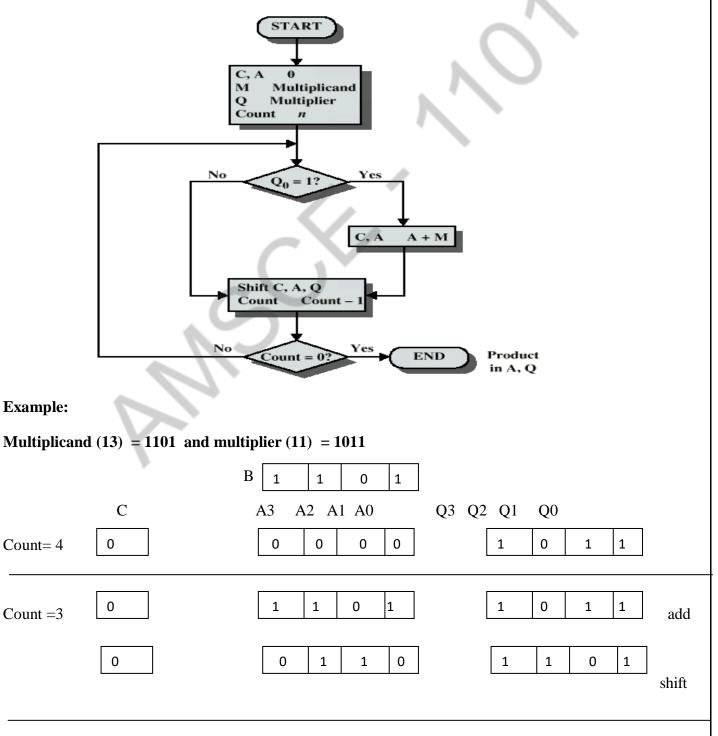

### Flow chart: (Algorithm)

Step1: Load multiplicand and multiplier in B and Q register and set zero initially to A & C registers.

Step 2: check Q register

Step 3: If  $Q_0 = 1$ , then add multiplicand and partial product and then shift all the bits of

A, C, Q in right side of one bit. So, C bit goes to  $A_{n-1}$ ,  $A_0$  goes to  $Q_{n-1}$  and  $Q_0$  is

lost.

If  $Q_0 = 0$ , shift all the bits of A, C, Q register in right side of one bit (no need for addition)

Step 4: Repeat the step2 and step3 in n times to get the desired result in the A & Q

### register.

| Count=2<br>add | 1 | 0 0 1 1 1 1 0 1 |

|----------------|---|-----------------|

|                | 0 | 1 0 0 1 1 1 0   |

| shift          |   |                 |

| Count =1       | 0 | 0 1 0 0 1 1 1 1 |

| shift          |   |                 |

| Count=0        | 1 | 0 0 0 1 1 1 1   |

| add            |   |                 |

| Shift          | 0 | 1 0 0 0 1 1 1 1 |

| ~              |   |                 |

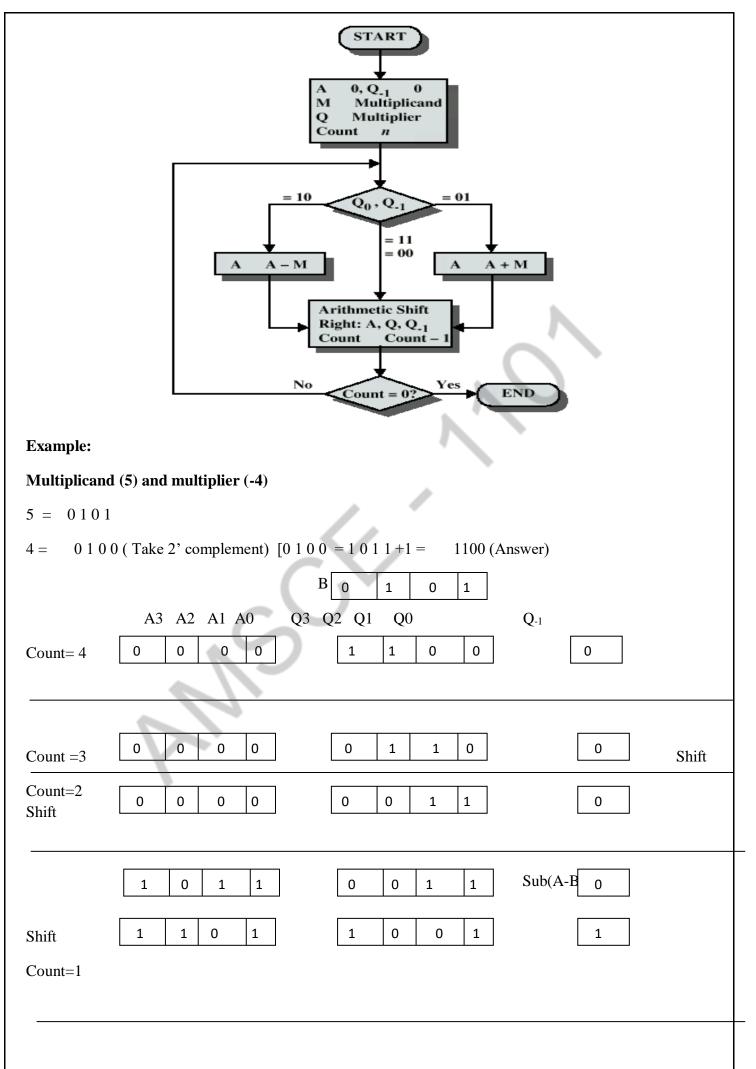

# (ii)Signed(negative) multiplication - Booth's Algorithm :

- > A powerful algorithm for sign multiplication is a booth algorithm.

- This algorithm used to reduce number of operations required for multiplication by representing multiplier as a difference between 2 numbers.

# Three Schemes used in Booth's Algorithm:

- (i).Booth algorithm recording schemes

- (ii)Hardware implementation of booth's algorithm

- (iii)Bit pair recording schemes

# (i).Booth algorithm recording schemes:

- $\succ$  +1 times the shifted multiplicand is selected when moving from 0 to 1.

- $\succ$  -1 times the shifted multiplicand is selected when moving from 1 to 0.

- $\succ$  0 times the shifted multiplicand is selected none of the above two cases.

- > Implies 0 to right of the multiplier LSB.

### **Example:**

$1\; 0\; 1\; 1\; 0\; 0 \\$

0 implied zero

-1 1 0 -1 0 0 (record multiplier using right shift)

# Example: Multiply 0 1 1 1 0 (+14) and multiplier 1 1 0 1 1 (-5)

11011

0 nd record multiplier, apply implied 0 and shift the bit)

0 -1 1 0 -1 // record multiplier

Perform multiplication:

0 1 1 1 0 (+14)

0 -1 1 0 -1 (record multiplier of (-5))

1 1 1 1 1 1 0 0 1 0  $\leftarrow$  2's complement (-1 means take 2's complement of multiplicand)

0 0 0 0 0 0 0 0 0 X

- 0 0 0 1 1 1 0 X X

- 1 1 0 0 1 0 X X X  $\leftarrow$  2's complement

- 0 0 0 0 0 X X X X X

- 1 1 0 1 1 1 0 1 0 (-70)

14 \* -5 =-70

-70 take 2's complement

256 128 64 32 16 8 4 2 1

- $0 \quad 0 \quad 1 \quad 0 \quad 0 \quad 1 \quad 0 \quad 0 \quad -70$

- 1 1 0 1 1 1 0 1 1  $\leftarrow$  1's complement

$+1 \leftarrow 2$ 's complement

1 1 0 1 1 1 0 1 0 (-70)

### (ii)Hardware implementation of booth's algorithm:

### Flow chart: (algorithm)

The sequence of events in booth's algorithm can be explained with the help of flowchart and algorithm.

Step 1: Load multiplicand and multiplier B and Q register and initially set zero in A &

Q-1 register

Step 2: check the status of  $Q_0$ ,  $Q_{-1}$ ,

if  $Q_0 Q_{-1} = 10$  perform A  $\leftarrow$  A- B

if  $Q_0 Q_{-1} = 01$  perform  $A \leftarrow A + B$

if  $Q_0 Q_{-1} = 00$  or 11 perform shift operation

Step 3: Arithmetic shift right operation perform from A,Q,Q<sub>-1</sub> registers. And decrement Sequence Count (SC) by 1.

Step 4: check count. If count is zero end the process. Else repeat steps 2 and 3

| Count = 0     1     1     1     0     | 1 |

|---------------------------------------|---|

| Shift                                 |   |

|                                       |   |

| <b>Final product :</b> 11101100 (-20) |   |

| <b>4 * 5 = 20</b> 0 0 0 1 0 1 0 0     |   |

| 1's complement 1 1 1 0 1 0 1 1        |   |

| 2's complement 1                      |   |

| 1 1 1 0 1 1 0 0                       |   |

### (iii)Bit pair recording schemes:

- > To speed up the multiplication process in the Booth's algorithm a technique called bit pair recording.

- > It is also called modified Booth's algorithm.

- > Booth recorded multiplier bits are grouped in pairs.

Steps:

- > implies zero in multiplier and perform right shift operation get the recoding multiplier

- ➢ if -1 perform 2 complement of multiplicand

- $\blacktriangleright$  if +2 perform left shift operation

- ➢ if -2 perform left shift operation and take 2'compelment you get the rsult

# Truth table:

| i+1 | i | i-1 | add  |

|-----|---|-----|------|

| Ο   | Ο | 0   | 0*M  |

| Ο   | Ο | 1   | 1*M  |

| Ο   | 1 | Ο   | 1*M  |

| Ο   | 1 | 1   | 2*M  |

| 1   | Ο | ο   | -2*M |

| 1   | ο | 1   | -1*M |

| 1   | 1 | Ο   | -1*M |

| 1   | 1 | 1   | 0*M  |

Example: 15 \* -10 [15 = 01111, -10 = 10110]

0 1 1 1 1 (+15)

-1 +2 -2 (record multiplier of (-10))

1 1 1 1 1 1 0 0 0 1 0  $\leftarrow$  (-2 : left shift and take 2's complement of multiplicand)

$0 \ 0 \ 0 \ 1 \ 1 \ 1 \ 1 \ 0 \ X \ \leftarrow (+2 : left shift of multiplicand)$

1 1 0 0 0 1 X X X X (-1 : 2's complement)

1 1 0 1 1 0 1 0 1 0 (-150)

Note: Any one algorithm you can write either positive or negative

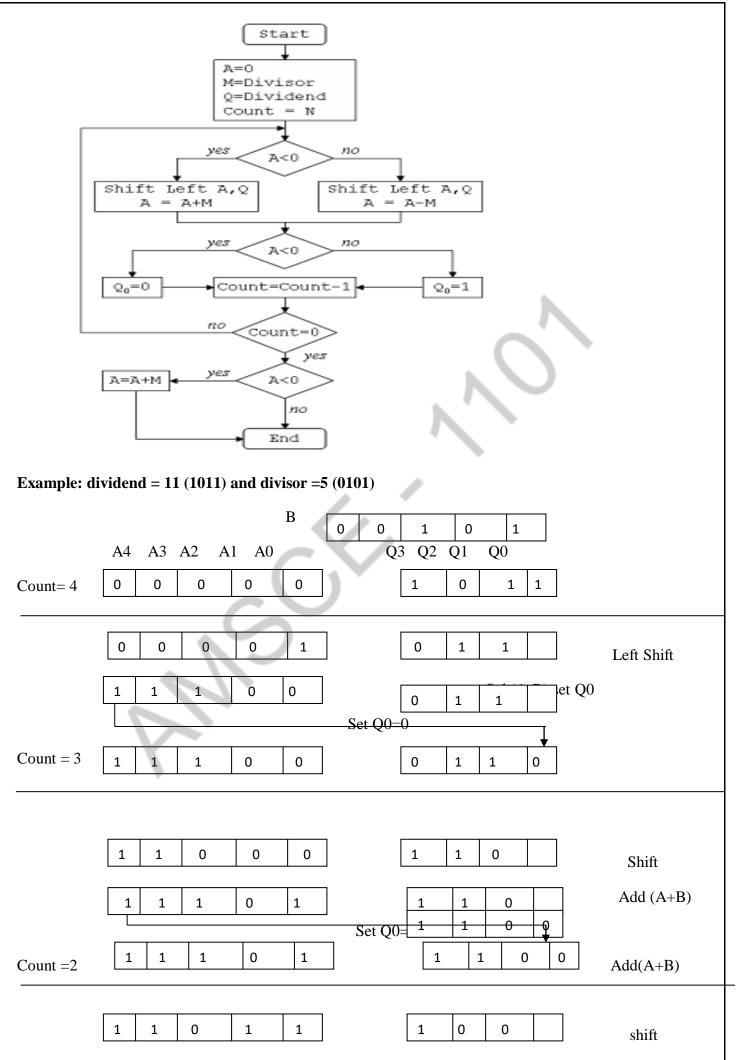

# 2. Discuss in detail about Division algorithm in detail with diagram and examples. NOV/DEC 2015, NOV/DEC 2014, APR/MAY 2017, APR/MAY 2018, NOV/DEC 2019

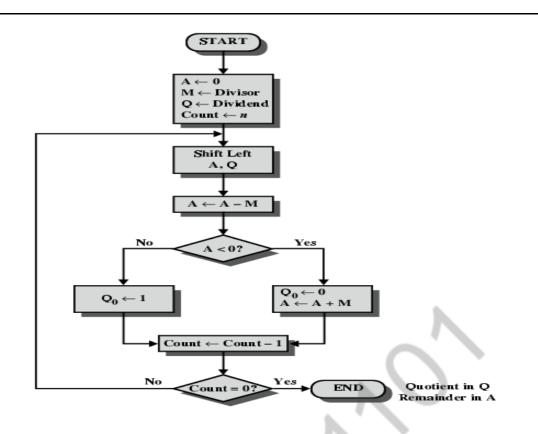

# **Types of division Algorithm:**

- 1. Restoring Division Algorithm.

- 2. Non Restoring Division Algorithm.

# **Restoring Division Algorithm:**

- > The hardware implementation for resorting division.

- > It consists of n+1 bit binary adder, shift, add and subtract control logic and registers A, B & Q

- > Dividend and divisor are loaded into register B and Register Q.

- Register A is initially set to zero

- Division operation is carried out.

- > After the division is completed, the n bit quotient is in register & the remainder is in register A.

# Flow chart:

Step 1: Load dividend and divisor Q and B register and initially set zero in A register

Step 2: Shift A & Q left one binary position

Step 3: Subtract divisor (add 2's complement of divisor (B)) from A & place answer back in A (A← A-B)

Step 4: In the sign bit of A is 1, set Q0 to 0 & add divisor back to A (that is , resorted); otherwise , set q0 to 1.

Step 5: Repeat steps 2 and 4 n times.

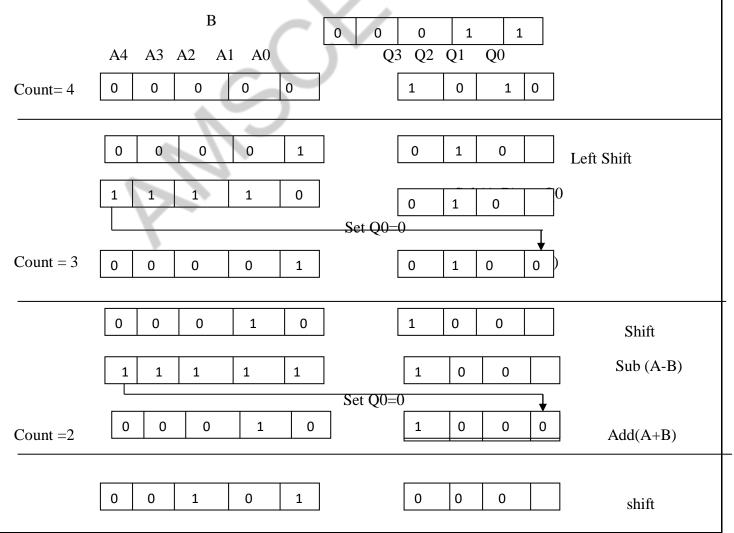

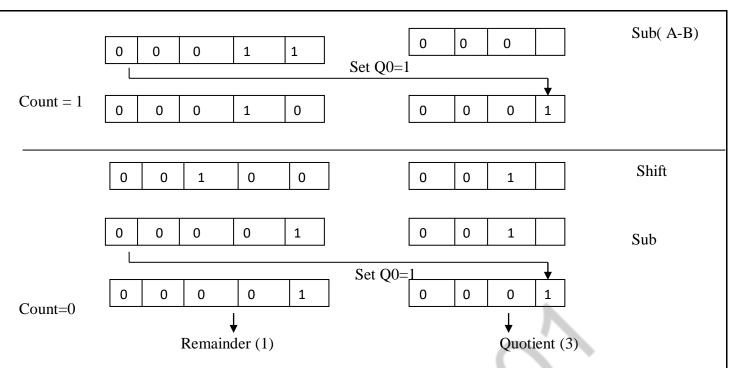

#### **Example:**

Dividend = 10 (1010)

Divisor = 3 (0011) ( if it is negative value take Take two complements (  $0\ 0\ 1\ 1=1\ 1\ 0\ 0\ +1=1\ 1\ 0\ 1$  )

## **Final product :** (10/3) remainder =1 and quotient = 3

### Non – Restoring Division Algorithm:

- > The hardware implementation for resorting division.

- ➤ It consists of n+1 bit binary adder, shift, add and subtract control logic and registers A, B & Q.

### Draw Restoring Division algorithm diagram:

- > Dividend and divisor are loaded into register B and Register Q.

- Register A is initially set to zero

- Division operation is carried out.

- > After the division is completed, the n bit quotient is in register & the remainder is in register A.

### Flow Chart:

Step 1: Load dividend and divisor Q and B register and initially set zero in A register

Step 2: If the sign bit of A is 0, shift A and Q left one bit position and subtract division from

A; otherwise, shift A and Q left and add divisor to A. If the sign bit of A is 0 set  $Q_0$  to 1

; otherwise set  $Q_0$  to 0Shift A & Q left one binary position

Step 3:Repeat steps 1 and 2 for n times.

Step 4: In the sign bit of A is 1, add divisor to A.

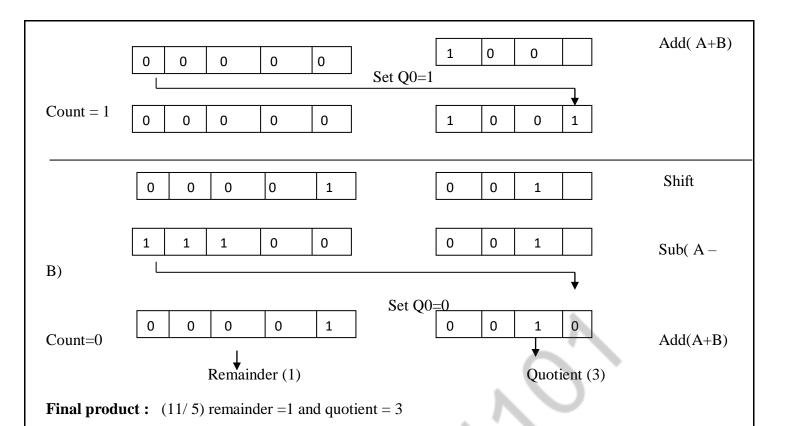

# **3. Expain how Floating Point operations carried out in a computer system.** APR/MAY 2016, APR/MAY 2015, APR/MAY 2017, APR/MAY 2018, NOV/DEC 2019

The binary point is said to float and the number s are called floating point number.

### It has represented 3 fields:

- Computers use a form of scientific notation for floating-point representation

- Computer representation of a floating-point number consists of three fixed-size fields:

- Sign Field : The one-bit sign field is the sign of the stored value.

- Exponents Field: The size of the exponent field determines the range of values that can be represented.

- Significant Field : The size of the significant determines the precision of the representation.

### **Two precisions:**

- 1. Single precision

- 2. Double precision

#### Single precision:

> The IEEE-754 single precision floating point standard occupies a single 32 bit words.

| 31                                                                                                                                                                                   | 30                                   | 22                      | 0 |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------|---|--|--|

| S                                                                                                                                                                                    | E'                                   | М                       |   |  |  |

| S: sign of n                                                                                                                                                                         | umber. 0- signifies +ve, 1- signifie | s –ve                   |   |  |  |

| E': 8 bit signed exponent in excess-127 representation.                                                                                                                              |                                      |                         |   |  |  |

| M : 23 bit n                                                                                                                                                                         | M: 23 bit mantissa fraction          |                         |   |  |  |

| Double prec                                                                                                                                                                          | ision:                               |                         |   |  |  |

| ► The I                                                                                                                                                                              | EEE-754 double precision occupie     | es a two 32 bit words.  |   |  |  |

| 63                                                                                                                                                                                   | 62                                   | 52 51                   | 0 |  |  |

| S                                                                                                                                                                                    | E'                                   | М                       |   |  |  |

| <ul> <li>S : sign of number. 0- signifies +ve, 1- signifies -ve</li> <li>E' : 11 bit signed exponent in excess-1023 representation.</li> <li>M : 52 bit mantissa fraction</li> </ul> |                                      |                         |   |  |  |

| 1.Floating p                                                                                                                                                                         | oint Addition and subtraction        |                         |   |  |  |

| Consider 2 fl                                                                                                                                                                        | oating point numbers                 | $\langle \cdot \rangle$ |   |  |  |

| A = m1. Re 2                                                                                                                                                                         |                                      |                         |   |  |  |

| B = m2. R e2                                                                                                                                                                         |                                      |                         |   |  |  |

| Rules for addition and subtraction:                                                                                                                                                  |                                      |                         |   |  |  |

| Step 1: select the number with smaller exponent & shift its mantissa right equal to the difference in exponent.                                                                      |                                      |                         |   |  |  |

| Step 2: set the exponent of the result equal to the larger exponent.                                                                                                                 |                                      |                         |   |  |  |

| Step3: perform addition or subtraction on the mantissa and determine the sign of the result.                                                                                         |                                      |                         |   |  |  |

| Step 4: Normalize the result if necessary.                                                                                                                                           |                                      |                         |   |  |  |

Step 5: round the number ( 4 digits long)

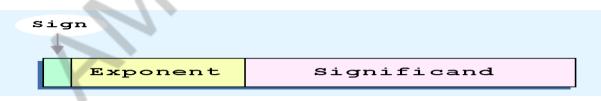

Flow chart:

## **FP Adder Hardware:**

The harware implementation for the addition and subtraction of 32 bit floating point operation.

1 bit sign, 8 bits for exponent and 23 bits for mantissa.

- > The steps of flow chart correspond to each block, from top to bottom.

- First, the exponent of one operand is subtracted from the other using the small ALU to determine which is larger and by how much.

- This difference controls the three multiplexors; from left to right, they select the larger exponent, the significand of the smaller number, and the significand of the larger number. The smaller significand is shifted right, and then the significands are added together using the big ALU.

- > The normalization step then shift s the sum left or right and increments or decrements the exponent.

- Rounding then creates the final result, which may require normalizing again to produce the actual final result.

**Example:** Add the number 1.75 X 10  $^2$  and 6.8 X 10  $^4$

step 1:

$1.75 \times 10^{2}$  (select the smaller exponent)

$0.175 \times 10^3$  (shift the point right and increment the power by 1)

$0.0175 \times 10^{4}$  (shift the point right and increment the power by 1)

Step 2 : Addition of the significance (mantissa)

Step 3: Normalize the result

6.8 1 7 5 X 10  $^4$

Step 4: round of the sum

6.8 1 8 X 10  $^{\rm 4}$

### Example: Subtract the number 0.5 ten and -0.4375 ten

# **Convert decimal to binary first:**

$0.5 \ X \ 2 = 1.0$

0.1 X 2  $^{0}$  (shift the point left and decrement the power by 1)

# 1.0 X 2<sup>-1</sup>// normalization

- 0. 0111 x 2  $^{0}$  (shift the point left and decrement the power by 1)

# - 1.11 X 2 <sup>-2</sup> // normalization

step 1: - 1.110 X 2<sup>-2</sup> (select the smaller exponent)

- 0.111 X 2<sup>-1</sup> (shift the point right and increment the power by 1)

# Step 2 : Addition of the significant (mantissa)

1.000 X 2<sup>-1</sup>// normalization

- 0.111 X 2<sup>-1</sup> // take 2' complement answer // 1.001)

Add the number:

1.000 X 2<sup>-1</sup>

1.001 X 2<sup>-1</sup>

$1 \ \overline{0.001 \ \mathbf{X} \ 2^{-1}}$  [discard the carry)

# **Step 3: Normalize the result**

0.001 **X 2**<sup>-1</sup> (shift the point left and decrement the power by 1)

00.01 **X 2**<sup>-2</sup> (shift the point left and decrement the power by 1)

000.1 **X 2 <sup>-3</sup>**

1.00 X 2<sup>-4</sup>

Step 4: round of the sum: 1.00 X 2<sup>-4</sup>

# **2.Floating point multiplication:**

Rules for Multiplication:

Step 1: Adding the exponent without bias and with bias. And subtract new exponents with bias and bias(127)

Step 2 : multiplication of significant.

Step 3: normalize the result

Step 4: round the product.

Step 5: place the sign in the final product

**Example:** multiply the number  $1.110 \times 10^{10}$  and  $9.200 \times 10^{-5}$

step 1: Add two exponents without bias

10 + (-5) = 5

Add two exponents with bias (127)

10 + 127 = 137

-5 + 127 = 122

Add 259

Subtract both new exponents with bias and bias(127):

259 - 127 = 132

Step 2: Multiply the significance (1.110 \* 9.200)

1110

9200

0000

0000x

2220xx

9990xxx

10212000

**Product is 10.212000 x10**<sup>5</sup> (place the point and add the exponent)

**Step 3: normalize the result:**

10.212000 x 10  $^{\rm 5}$

1.0212000 x 10<sup>6</sup>

**Step 4: round the result:**

1.0212 x 10<sup>6</sup>

**Step 5: place the sign in the product:**

+ 1.0212 x 10  $^{6}$

Example: multiply the number 0.5 ten and -0.4375 ten

### Convert decimal to binary first:

0.5 X 2 = 1.0

0.1 X 2  $^{0}$  (shift the point left and decrement the power by 1)

# 1.0 X 2<sup>-1</sup>// normalization

- 0. 0111 X 2  $^{0}$  (shift the point left and decrement the power by 1)

# - 1.11 X 2 <sup>-2</sup> // normalization

step 1: Add two exponents without bias

$$-1 + (-2) = -3$$

Add two exponents with bias (127)

-1 + 127 = 126

$$-2 + 127 = 125$$

Add 251

Subtract both new exponents with bias and bias(127):

251 - 127 = 124

Step 2: Multiply the significance (1.0 \* 1.11)

1.11

10

1.110

**Product is 1.110 x10**<sup>-3</sup> (place the point and add the exponent)

**Step 3: normalize the result:**

1.110 x10 <sup>-3</sup>

**Step 4: round the result:**

$1.110 \text{ x} 10^{-3}$

### **Step 5: place the sign in the product:**

- 1.110 x10 <sup>-3</sup>

# **3.Floating point Division:**

Step 1: Subtract the exponent without bias and with bias. And add new exponents with bias and bias (127)

Step 2 : Divide the significant.

Step 3: normalize the result

Step 4: round the product.

Step 5: place the sign in the final product

**Example:** divide the number  $1.110 \times 10^7$  and  $9.200 \times 10^{-5}$

step 1: sub two exponents without bias

7 - (-5) = -12

sub two exponents with bias (127)

7 - 127 = -120

-5 - 127 = -132

Sub 12 (-120)-(-132)=(-120 + 132) = 12

Add both new exponents with bias and bias(127):

$$12 + 127 = 139$$

Step 2: Divide the significance (1.110 / 9.200)

After normal division the answer is  $= 0.1206 \times 10^{-12}$

Product is 10.212000 x10<sup>5</sup> (place the point and add the exponent)

#### **Step 3: normalize the result:**

0.1206 x 10<sup>-12</sup>

1.206 x 10<sup>-13</sup>

**Step 4: round the result:**

1.20 x 10<sup>-13</sup>

#### **Step 5: place the sign in the product:**

+1.20 x 10<sup>-13</sup>

#### **UNIT-III PROCESSOR AND CONTROL UNIT**

#### 1. What is meant by data path element? NOV/DEC 2019

A data path element is a unit used to operate on or hold data within a processor. In the MIPS implementation, the data path elements include the instruction and data memories, the register file, the ALU, and adders.

#### 2. What is the use of PC register?

Program Counter (PC) is the register containing the address of the instruction in the program

being executed.

#### 3. What is meant by register file?

The processor's 32 general purpose registers are stored in a structure called a register file. A register file is a collection of registers in which any register can be read or written by specifying the number of the register in the file. The register file contains the register state of the computer.

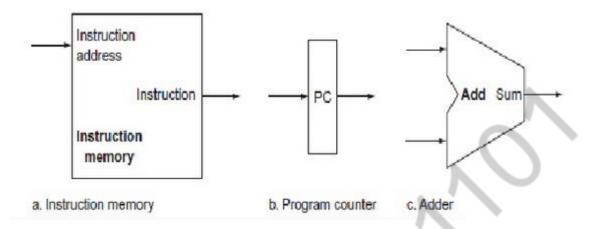

4. What are the two state elements needed to store and access an instruction?

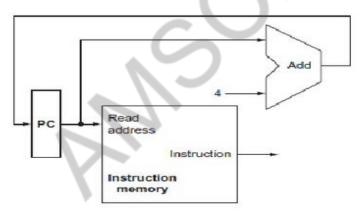

Two state elements are needed to store and access instructions, and an adder is needed to compute the next instruction address. The state elements are the instruction memory and the program counter.

#### 5. Draw the diagram of portion of data path used for fetching instruction.

A portion of the data path is used for fetching instructions and incrementing the program counter. The fetched instruction is used by other parts of the data path

#### 6. Define Sign Extend

Sign-extend is used to increase the size of a data item by replicating the high-order sign bit of the original data item in the high order bits of the larger, destination data item.

#### 7. What is meant by branch target address?

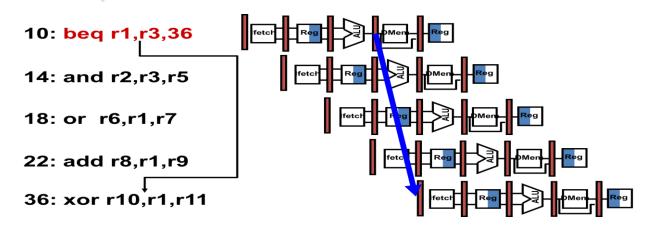

Branch target address is the address specified in a branch, which becomes the new program counter (PC) if the branch is taken. In the MIPS architecture the branch target is given by the sum of the off set field of the instruction and the address of the instruction following the branch.

#### 8. Differentiate branch taken from branch not taken.

Branch taken is a branch where the branch condition is satisfied and the program counter (PC) becomes

the branch target. All unconditional jumps are taken branches. Branch not taken or (untaken branch) is a branch where the branch condition is false and the program counter (PC) becomes the address of the instruction that sequentially follows the branch.

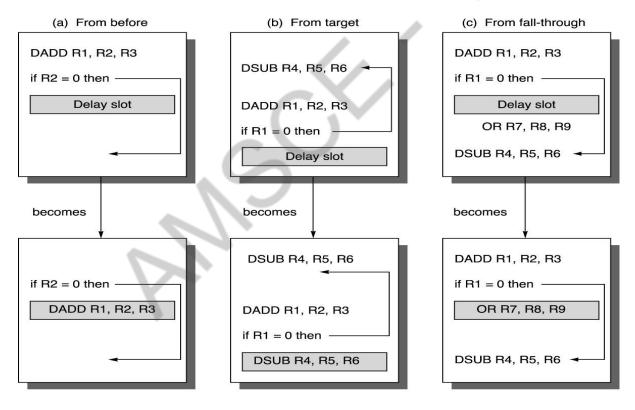

# 9. What is meant by delayed branch?

Delayed branch is a type of branch where the instruction immediately following the branch is always executed, independent of whether the branch condition is true or false

# 10. What are the three instruction classes and their instruction formats?

The three instruction classes (R-type, load and store, and branch) use two different instruction formats.

# **11.** Write the instruction format for the jump instruction.

The destination address for a jump instruction is formed by concatenating the upper 4 bits of the current PC + 4 to the 26-bit address field in the jump instruction and adding 00 as the 2 low-order bits.

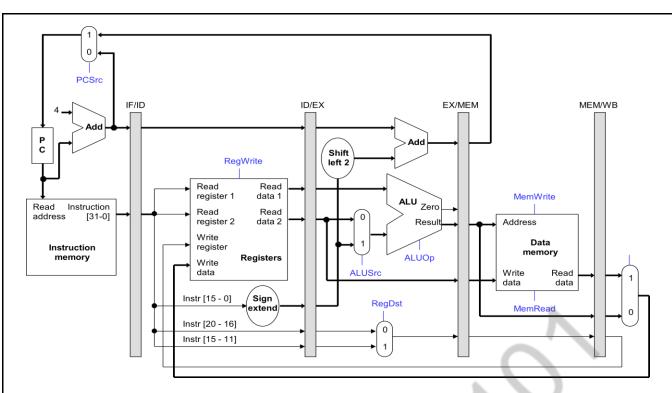

# 12. What is meant by pipelining? [May 2016]

Pipelining is an implementation technique in which multiple instructions are overlapped in execution. Pipelining improves performance by increasing instruction throughput, as opposed to decreasing the execution time of an individual instruction.

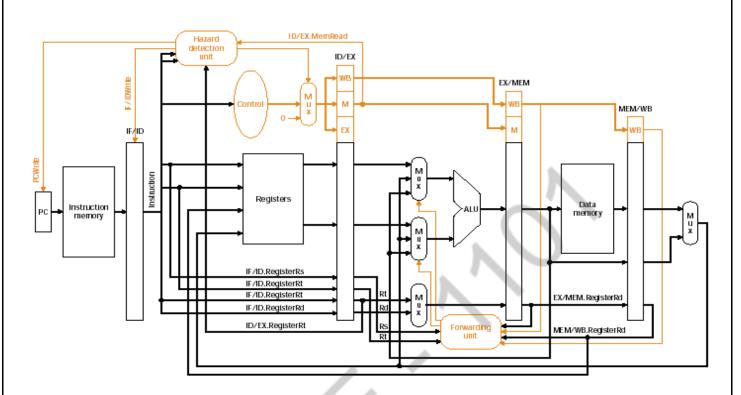

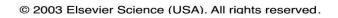

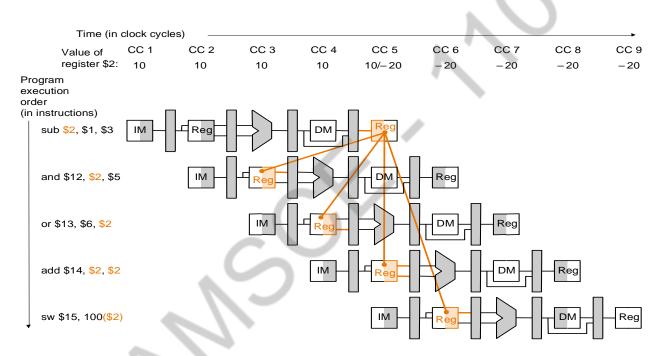

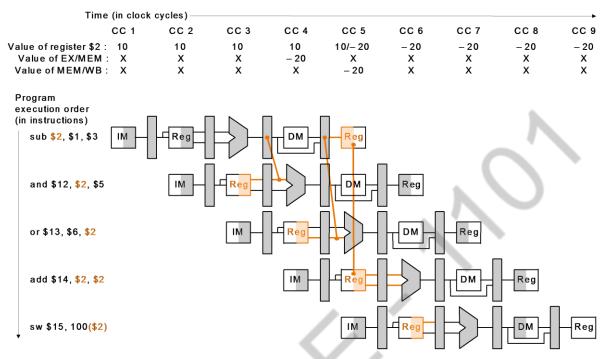

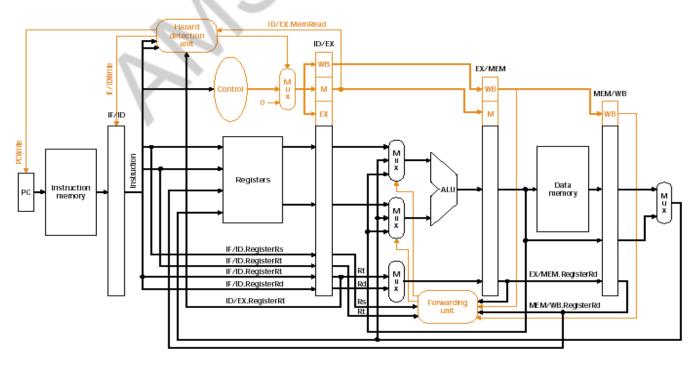

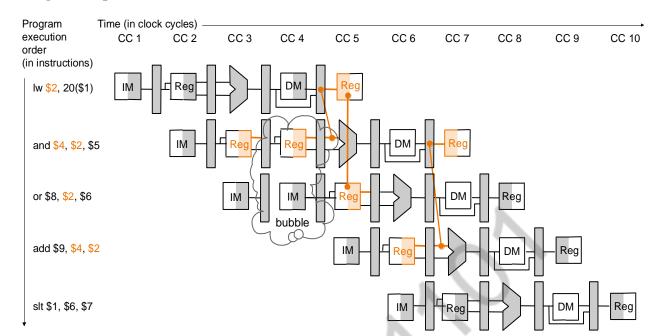

# 13. What is meant by forwarding?

Forwarding, also called bypassing, is a method of resolving a data hazard by retrieving the missing data element from internal buffers rather than waiting for it to arrive from programmer visible registers or memory.

# 14. What is pipeline stall?

Pipeline stall, also called bubble, is a stall initiated in order to resolve a hazard. They can be seen elsewhere in the pipeline.

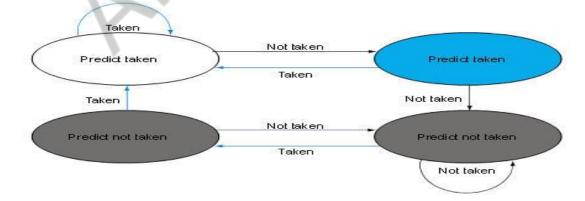

# 15. What is meant by branch prediction?[May 2015/Dec 2015]

Branch prediction is a method of resolving a branch hazard that assumes a given outcome for the branch and proceeds from that assumption rather than waiting to ascertain the actual outcome.

# 16. What are the five steps in MIPS instruction execution?

1. Fetch instruction from memory.

2. Read registers while decoding the instruction. The regular format of MIPS instructions allows reading and decoding to occur simultaneously.

- 3. Execute the operation or calculate an address.

- 4. Access an operand in data memory.

- 5. Write the result into a register.

### 17. Write the formula for calculating time between instructions in a pipelined processor?

Time between instructions<sub>pipelined</sub> =  $\frac{\text{Time between instruction}_{nonpipelined}}{\text{Number of pipe stages}}$

#### 18. What are hazards? Write its types. [Dec 2015]

There are situations in pipelining when the next instruction cannot be executed in the following clock

cycle. These events are called hazards, and there are three different types.

- 1. Structural Hazards

- 2. Data Hazards

- 3 . Control Hazards

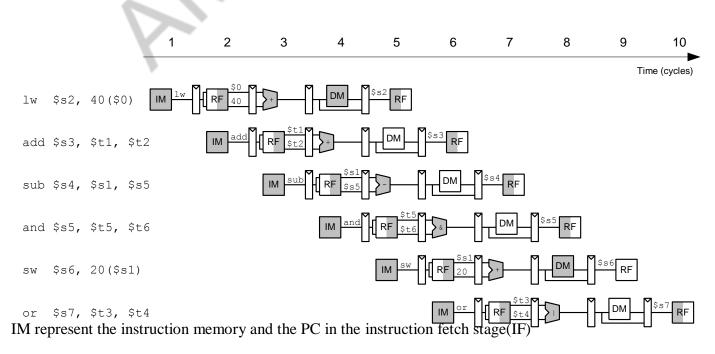

### 19. What are the 5 pipeline stages?

The 5 stages of instruction execution in a pipelined processor are:

- 1. IF: Instruction fetch

- 2. ID: Instruction decode and register file read

- 3. EX: Execution or address calculation

- 4. MEM: Data memory access

- 5. WB: Write back

#### 20. What are exceptions and interrupts?[Dec 2014/May 2016]

Exception, also called interrupt, is an unscheduled event that disrupts program execution used to detect overflow. Eg. Arithmetic overflow, using an undefined instruction. Interrupt is an exception that comes from outside of the processor.Eg. I/O device request

#### 21. Define - Vectored Interrupts

Vectored interrupt is an interrupt in that the address to which the control is transferred is determined by the cause of the exception

# PART-B

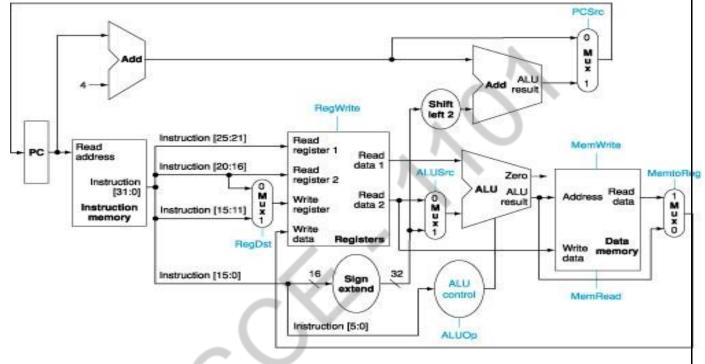

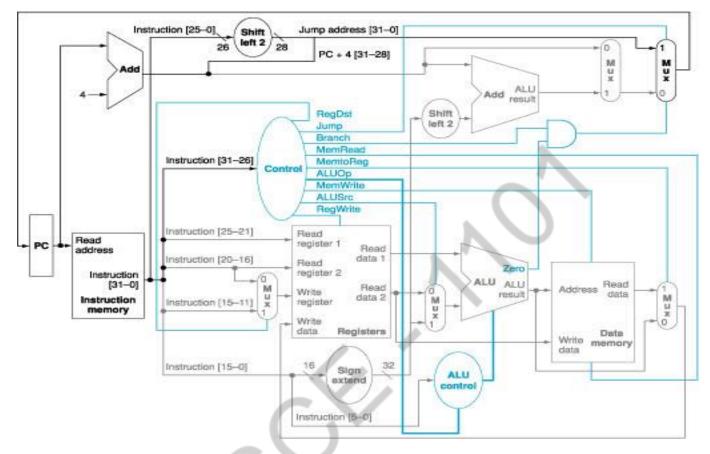

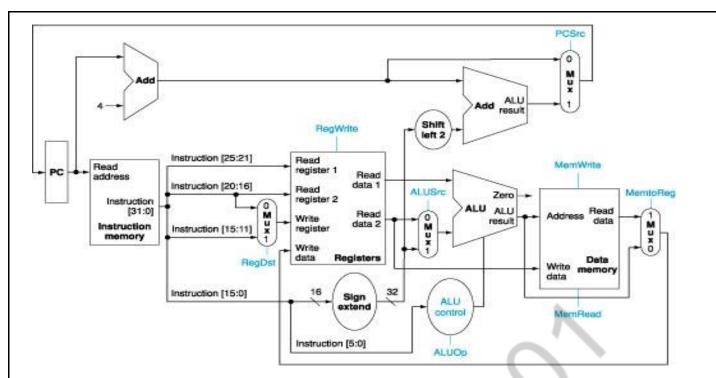

# 1.ExplainthebasicMIPSimplementationofinstructionsetNOV/DEC 2015, APR/MAY 2015, APR/MAY 2019(16 MARKS )BASICMIPS IMPLEMENTATION:

The basic MIPs implementation includes a subset of the core MIPS instruction set.

Every instructions are divided into 3 instruction classes

#### Instruction classes:

- 1. Memory Reference Instruction. [load word and store word]

- 2. Arithmetic and logical instruction [ Add, Sub, mul, Or, And ect]

- 3. Branch instruction. [jump and branch equal]

# **Overview of the MIPS implementation:**

In every instruction, there are two steps which are identical

- 1. Fetch instruction: fetch the instruction from the memory

- 2. Fetch operand: select the registers to read

# **Operation:**

The program counter: It supply instruction address to the instruction memory.

**Instruction memory:** After the instruction is fetched, the register operands required by an instruction are specified by fields of that instruction

**Register operand:** Once the register operands have been fetched, they can be used to compute three classes of instruction.

# 1. Memory Reference Instruction:

- ➢ It uses the ALU for an address calculation.

- After using ALU, memory reference instruction to access the memory either to read data for a load or write data for a store.

# 2. Arithmetic and logical instruction:

- ➢ It uses ALU for the operation execution.

- After completing the execution the Arithmetic and logical instruction must write the data from ALU or memory back into a register.

# 3. Branch instruction:

- ➢ It uses ALU for comparison.

- After comparison, need to change the next instruction address based on the comparison, otherwise Pc should be incremented by 4 to get the address of next instruction.

**Multiplexor:** The data going to a particular unit comes from two different sources. These data lines cannot be wired together, we must add a device that combine the multiple sources and sent to the destination. Such device called multiplexor (many inputs single output)

Adder: Increment the PC to the address of the next instruction.

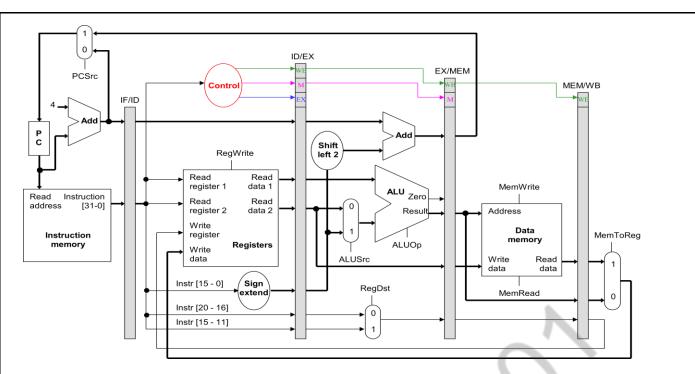

# **Basic implementation of MIPS with Control signals:**

The multiplexor selects from several inputs' based on the setting of its control lines.

The control lines are set Based on information taken from the instruction being execute.

# **Control unit:**

Control unit which has the instruction as an input is used to determine the control signals for the function unit and two of the multiplexors.

- > The input to the control fields is the 6 bit opcode field from the instruction.

- > The output of the control unit consist of three 1-bit signals are used to control multiplexors.

- ➢ 3 signals for controlling reads and writes in the register file and data memory.

- > 1-bit control signal used in determining for branch

- > 2-bit control signal for ALU.

# Logic Design Conventions:

In MIPS implementation consists of two different types of logic elements (data path element).

- 1. Combinational Element

- 2. State Element

# **Combinational Element:**

The element that operates on data value such as AND gate or an ALU, which means the output depend only on the current inputs.

# **State Element:**

- A memory element such as register or a memory is called as state element.

- > An element contains state if it has internal storage.

- Logical component that contains state are called sequential, because their output depend on both their inputs and the contents of the internal state.

# **Clocking Methodology:**

- > It is used to determine when the data is valid and stable relative to the clock.

- ➢ It specifies the timing of read and writes.

- > A clocking methodology is designed to ensure predictability.

### Edge – triggered clocking Methodology:

> Any values stored in a sequential logic element are updated only on a clock edge.

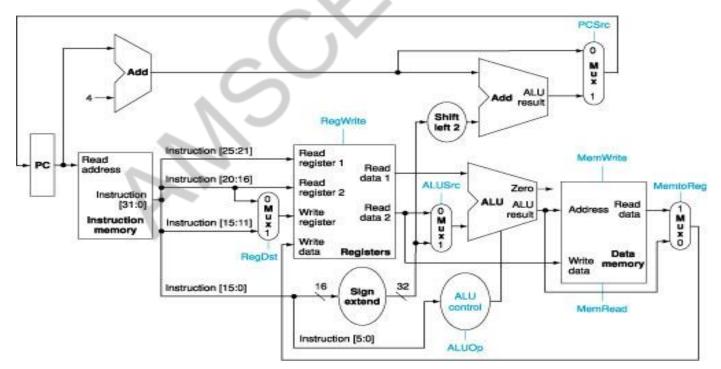

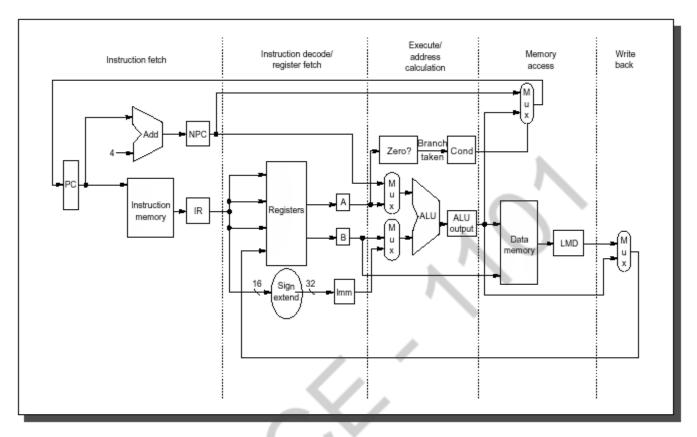

# 2. Explain in detail about building a data path [Dec 2014 ], APR/MAY 2018,NOV/DEC 2019

# **BUILDING DATA PATH:**

A data path element is used to operate on or hold data within a processor.

In MIPS implementation, the data path elements include the instruction and data memories, the register files, the ALU and adders.

**Instruction Memory:** A memory unit to store the instruction of a program and supply instructions gives an address.

**Program counter:** PC is register containing the address of the next instruction in the program.

Adder: Increment the Pc to the address of the next instruction.

#### Data segments:

There are three data Segments:

- 1. Data segment for Arithmetic and logical instruction.

- 2. Data segment for load word and store word instruction.

- 3. Data segment for branch instruction.

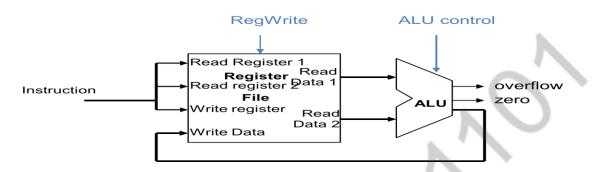

# 1.Data segment for Arithmetic and logic instruction:

- Arithmetic and logical instruction read operands from 2 registers, perform an Arithmetic and logical operation and write the result to the register.

- > These instruction are also called R-format instructions.

### **R-** format instruction:

- ▶ R- format instruction have three register operands. 2 source operand and 1 destination operand.

- ➢ It include add, sub, AND, OR and slt.

- ➢ Example: OR \$t1, \$t2, \$t3

# The register files:

- > In MIPS processor stores 32 general purpose register this structure called register file

- ➢ It is a collection of register.

- > It contains the register state of computer.

#### **Read registers:**

> To read data words, we need to specify the register number to the register file.

# Write Register: To write data words, we need two inputs.

- 1. To specify the register number to be written.

- 2. To supply the data to be written into the register.

#### **Register write:**

- > It is a write control signal.

- ➢ It control write operation.

- > If the signal is edge triggered, to perform write operation.

- > If the signal is earlier clock cycle, to perform read operation.

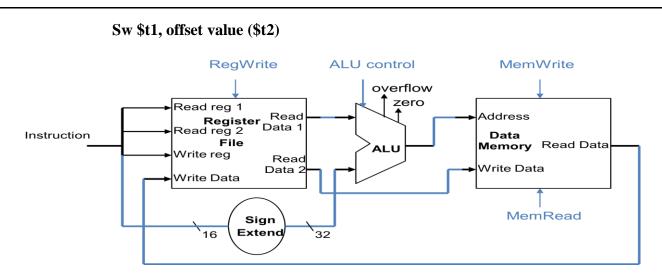

# 2.Data Segment for load word and store word instruction:

The general form of load word and store word instruction in MIPS processor are

# Lw \$ t1, offset value(\$t2)

These instruction compute memory address by adding the base register.

#### **Memory address = base register + offsetvalue.**

store value : read from the Register File , written to the Data Memory

load value : read from the Data Memory, written to the Register File

### Sign extend :

- > To convert 16 bits offset field in the instruction to a 32 bit signed value.

- It is used to increase the size of the data item by replacing the high order sign bit of the original data item in the higher order bit of the larger destination data item.

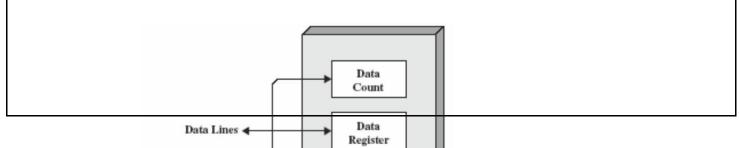

#### Data memory unit:

It has read and write control signal, an address input and an input for the data to be written into memory

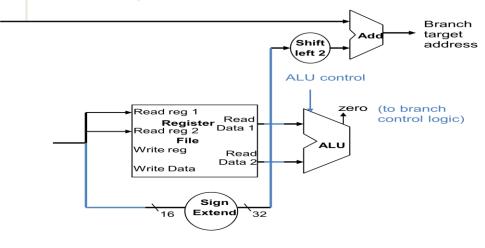

# **3.Data Segment for branch instruction:**

- > The branch instruction has three operands, 2 register & 1 offset.

- > 2 register are compared for equality (zero ALU output).

- > 16 bit offset used to compute branch target address.

- Branch target address is an address specified in a branch which becomes the new program counter if the branch is taken.

Example: beq \$t1, \$t2, offset

- > If the condition is true ,the branch target address becomes new pc and the branch is taken.

- > If the condition is false, incremented pc should replace the current pc and branch is not taken

# The branch data path must perform two operations:

1. Compute the branch target address: the branch data path includes a sign extension unit, shifter and an adder

2. Compare the register content : used register file and the ALU.

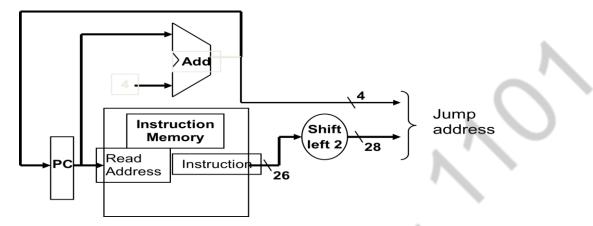

# Jump operation involves:

Replace the lower 28 bits of the PC with the lower 26 bits of the fetched instruction shifted left by 2 bits.

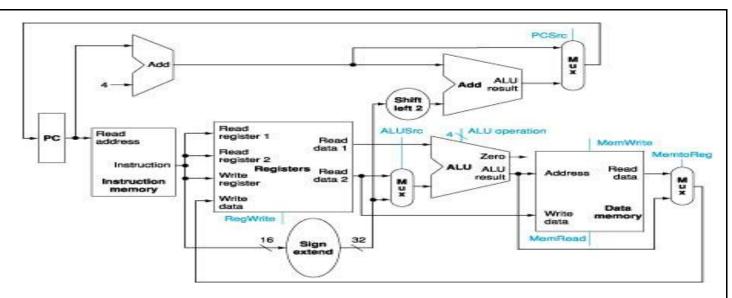

# Creating a single data path:

- > The data path component for individual instruction classes, combine them into a single data path and add the control to complete the implementation.

- The simplest data path will attempt to execute all instruction in one clock cycle (fetch, decode and execute each instructions in one clock cycle)

- > No data path resource can be used more than once per instruction.

- > Multiplexors needed at the input of shared elements with control lines to do the selection

- > Write signals to control writing to the Register File and Data Memory

- > Cycle time is determined by length of the longest path.

# Problem:

How to build a data path for the operational portion of the memory reference and arithmetic logical instructions that use a single register file and a single ALU to handle both types of instructions assign any necessary multiplexors.

**Answer:** to create a data path with only a single register file and a single ALU, we use two multiplexors. One is placed at the ALU input and another at the data input to the register file.

# Show how to built a datapath for arithmetic-logical ,memory reference and branch instructions.

We can combine all the pieces to make a simple data path for the MIPS architecture by adding the datapath for instruction fetch, the data path from R- format and memory instruction and the data path for branches.

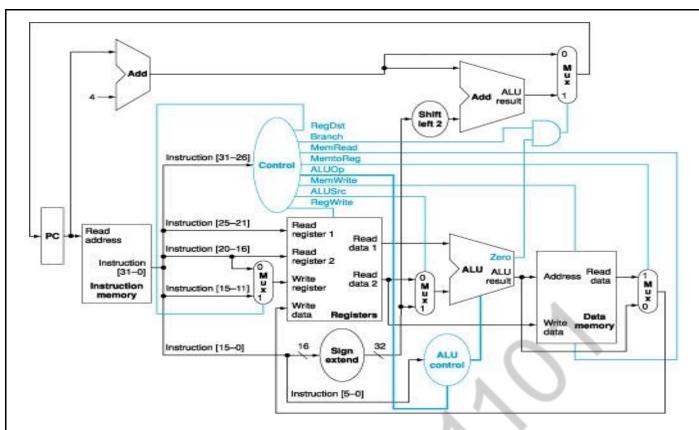

# 3. Explain in detail about control implementation scheme.[Dec 2014]

# **CONTROL IMPLEMENTATION SCHEME:**

A control implementation scheme by adding simple control functions to the existing data path.

# Different control implementation scheme:

- 1. The ALU control

- 2. Designing the main control unit

- 3. Operation of the datapath

# The ALU control:

There are 6 possible combinations of 4 control inputs. ALU will need to perform one of these function

| ALU control lines | Function         |

|-------------------|------------------|

| 0000              | AND              |

| 0001              | OR               |

| 0010              | add              |

| 0110              | subtract         |

| 0111              | set on less than |