MICROPROCESSORS

# AND

# MICROCONTROLLERS

(*EE6502*)

## FREQUENTLY ASKED QUESTIONS WITH ANSWERS

S.V.MAHESH KUMAR

## UNIT 1 8085 PROCESSOR

1. Describe in detail about the architecture of 8085. (May/Jun 2016, Nov/Dec 2015, Dec 2016)

The 8085 is a 8-bit general-purpose microprocessor (µp)

- Capable of addressing **64 k** of **memory**

- > Has 40 pins

- $\blacktriangleright$  Requires +5 v power supply

- Can operate with 3 MHz clock

#### Arithmetic Logic Unit

- The ALU performs the actual numerical and logic operation such as 'add', 'subtract', 'AND', 'OR', etc.

- Uses data from memory and from Accumulator to perform arithmetic. Always stores result of operation in Accumulator.

## Accumulator

- > The accumulator is an **8-bit register** that is a part of ALU.

- This register is used to store 8-bit data and to perform arithmetic and logical operations.

- > The result of an operation is temporarily stored in the accumulator. The accumulator is also known as as register A.

- > It is a **Special Purpose Register**.

#### Flag Register

- The ALU includes five flip-flops, which are set or reset after an operation according to data conditions of the result in the accumulator and other registers.

- They are called Zero (Z), Carry (CY), Sign (S), Parity (P), and Auxiliary Carry (AC) flags.

- The microprocessor uses these flags to test data conditions. They are shown in the Figure below.

|     | D4 | D3 | $D_2$ | $D_1$ | D <sub>0</sub> |

|-----|----|----|-------|-------|----------------|

| S 2 | AC |    | Р     |       | СҮ             |

- The above Figure shows an 8-bit register, called the flag register, adjacent to the accumulator. However, it is not used as a register; five bit positions out of eight are used to store the outputs of the five flip-flops.

- The flags are stored in the 8-bit register so that the programmer can examine these flags (data conditions) by accessing the register through an instruction.

- Sign Flag is used for indicating the sign of the data in the accumulator. The sign flag is set if negative (1 –negative). The sign flag is reset if positive (0 –positive).

- ➢ For example, after an addition of two numbers, if the sum in the accumulator is larger

than eight bits, the flip-flop uses to indicate a carry -- called the Carry flag (CY) is

to one.

- > When an arithmetic operation results in zero, the flip-flop called the Zero (Z) flag is set to one.

- Auxiliary Carry flag is set if there is a carry out of bit 3.

- > Parity flag is set if parity is even.

#### *Registers (General-Purpose)*

- The 8085/8080A has six general-purpose registers to store 8-bit data; these are identified as B,C,D,E,H, and L.

- > They can be combined as register pairs BC, DE, and HL to perform some 16-bit operations.

#### Program Counter (PC)

- > This 16-bit register deals with sequencing the execution of instructions. This register is a memory pointer. Memory locations have 16-bit addresses, and that is why this is a 16-bit register.

- > The function of the program counter is to point to the memory address from which the

Next byte is to be fetched.

When a byte (machine code) is being fetched, the program counter is incremented by one to point to the next memory location.

#### Stack Pointer (SP)

> The stack pointer is also a 16-bit register used as a memory pointer. It points to a memory location in R/W memory, called the stack.

## > LIFO

## Instruction Register/Decoder

> Temporary store for the current instruction of a program. Latest instruction sent here from memory prior to execution. Decoder then takes instruction and 'decodes' or interprets the instruction. Decoded instruction then passed to next stage.

#### 8085 System Bus

set

## Address Bus:

- > The address bus has 8 signal lines A8 –A15, which are unidirectional

- (ie) numbers only sent from microprocessor to memory, not other way. The other 8 address bits are multiplexed (time shared) with the 8 data bits.

## Data Bus:

- > It carries 'data', in binary form, between  $\mu P$  and other external units, such as memory.

- It is Bi-directional. the bits AD0 –AD7are bi-directional and serve as A0 –A7and D0 –D7at the same time.

- During the execution of the instruction, these lines carry the address bits during the early part, and then during the late parts of the execution, they carry the 8 data bits.

Control Bus:

Control Bus is various lines which have specific functions for coordinating and controlling uP operations

## Interrupt Control

- > The 8085A has5 interrupt inputs: INTR, RST5.5, RST6.5, RST 7.5, and TRAP.

- The interrupts are arranged in a fixed priority that determines which interrupt is to be recognized if more than one is pending as follows: TRAP highest priority, RST 7.5, RST 6.5, RST 5.5, INTR has lowest priority.

- > The TRAP interrupt is useful for **critical errors** such as **power failure** or **bus error**.

[Note: Refer Section 1.5 for more details]

#### Serial I/O Control

- SID (Serial input data) line -The data on this line is loaded into accumulator bit 7 whenever a RIM instruction is executed.

- SOD (Serial output data) line. The output SOD is set or reset as specified by the SIM instruction.

## Timing & Control

X1 and X2

- Crystal oscillator or R/C network connections are used to set the internal clock generator.

- > The input frequency is divided by 2 to give the internal operating frequency.

- Clock generator generates

## 3.125 MHz internally

## 6.25 MHz externally

## CLK (Output)

- Clock Output for use as a system clock when a crystal or R/C network is used as an input to the CPU.

- > The period of CLK is twice the X1, X2 input period

## ALE (Output)

- Address Latch Enable: It occurs during the first clock cycle of a machine state and enables the address to get latched into the on chip latch of peripherals.

- > The falling edge of ALE is set to guarantee setup and hold times for the address information

- > ALE can also be used to strobe the status information. ALE is never 3stated.

## SO, S1 (Output)

Data Bus Status. Encoded status of the bus cycle:

## S1 S0

0 0 HALT

| 0 | 1 | WRITE |

|---|---|-------|

| 1 | 0 | READ  |

| 1 | 1 | FETCH |

S1 can be used as an advanced R/W status.

## READ ( RD ) - (Output 3state)

READ; indicates the selected memory or 1/0 device is to be read and that the Data Bus is available for the data transfer.

## WRITE ( WR )-(Output 3state)

WRITE; indicates the data on the Data Bus is to be written into the selected memory or 1/0 location. Data is set up at the trailing edge of WR. 3stated during Hold and Halt modes.

## READY (Input)

If Ready is high during a read or write cycle, it indicates that the memory or peripheral is ready to send or receive data. If Ready is low, the CPU will wait for Ready to go high before completing the read or write cycle.

## HOLD (Input)

HOLD; indicates that another Master is requesting the use of the Address and Data Buses. When the Hold is acknowledged, the Address, Data, RD, WR, and IO/M lines are 3stated.

## HLDA (Output)

HOLD ACKNOWLEDGE; indicates that the CPU has received the Hold request and

that it will relinquish the buses in the next clock cycle.

HLDA goes low after the Hold request is removed. The CPU takes the buses one half clock cycle after HLDA goes low.

## RESET IN ( RESET IN )

Reset sets the Program Counter to zero and resets the Interrupt Enable and HLDA flip-flops. None of the other flags or registers (except the instruction register) are affected .The CPU is held in the reset condition as long as Reset is applied.

## RESET OUT

➤ Indicates CPU is being reset. Can be used as a system RESET. The signal is synchronized to the processor clock.

## <u>ю/М (IO/M)- (Output)</u>

IO/M indicates whether the Read/Write is to memory or I/O Tristated during Hold and

Halt modes.

<u>Vcc</u>

$\rightarrow$  +5 volt supply.

Vss

➢ Ground Reference.

\_\_\_\_\_

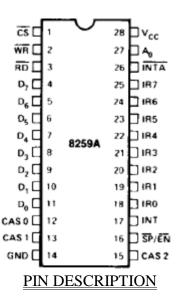

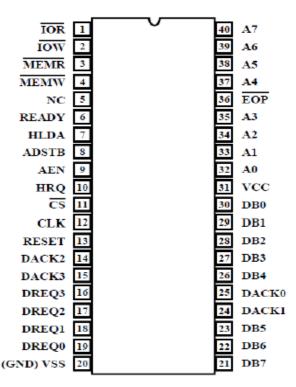

2. Describe the functional pin diagram of 8085. (May/June 2017)

## The description is given below

## X1 and X2 (Pin 1 & Pin 2)

- Crystal oscillator or R/C network connections are used to set the internal clock generator.

- > The input frequency is divided by 2 to give the internal operating frequency.

- Clock generator generates

## 3.125 MHz internally

## 6.25 MHz externally

CLK (Output)- ( Pin 37)

- Clock Output for use as a system clock when a crystal or R/C network is used as an input to the CPU.

- > The period of CLK is twice the X1, X2 input period

#### ALE (Pin 30)

$\succ$  Address Latch Enable: It occurs during the first clock cycle of a machine state and enables the address to get latched into the on chip latch of peripherals.

#### SO, S1 (Output)- (Pin 29 & Pin 33)

These are status signals .The functions are given below

S1 S0

HALT

0

0

HALT

1

1

WRITE

1

0

READ

1

1

FETCH

S1 can be used as an advanced R/W status.

#### <u>READ ( RD</u> ) (Pin 32)

READ; indicates the selected memory or 1/0 device is to be read and that the Data Bus is available for the data transfer.

#### <u>WRITE ( WR )(Pin 31)</u>

WRITE; indicates the data on the Data Bus is to be written into the selected memory or 1/0 location. Data is set up at the trailing edge of WR. 3stated during Hold and Halt modes.

#### READY (Input)-(Pin 35)

If Ready is high during a read or write cycle, it indicates that the memory or peripheral is ready to send or receive data. If Ready is low, the CPU will wait for Ready to go high before completing the read or write cycle.

#### HOLD (Input)-(Pin 39)

HOLD; indicates that another Master is requesting the use of the Address and Data Buses. When the Hold is acknowledged, the Address, Data, RD, WR, and IO/M lines are 3stated.

#### HLDA (Output)- (Pin 38)

HOLD ACKNOWLEDGE; indicates that the CPU has received the Hold request and

that it will relinquish the buses in the next clock cycle.

HLDA goes low after the Hold request is removed. The CPU takes the buses one half clock cycle after HLDA goes low.

## RESET IN ( RESET IN )- (Pin 36)

Reset sets the Program Counter to zero and resets the Interrupt Enable and HLDA flip-flops. None of the other flags or registers (except the instruction register) are affected .The CPU is held in the reset condition as long as Reset is applied.

## RESET OUT (Pin 3)

➢ Indicates CPU is being reset. Can be used as a system RESET. The signal is synchronized to the processor clock.

## **10/M** (Output)- (Pin 34)

IO/M indicates whether the Read/Write is to memory or I/O Tristated during Hold and

Halt modes.

## INTR (Input) - (Pin 10)

INTERRUPT REQUEST; is used as a general-purpose interrupt. It is sampled only during the next to the last clock cycle of the instruction. If it is active, the Program Counter (PC) will be inhibited from incrementing and an INTA will be issued. During this cycle a RESTART or CALL instruction can be inserted to jump to the interrupt service routine. The INTR is enabled and disabled by software. It is disabled by Reset and immediately after an interrupt is accepted.

## (Output) – (Pin 11)

INTERRUPT ACKNOWLEDGE; is used instead of (and has the same timing as) RD during the Instruction cycle after an INTR is accepted. It can be used to activate the 8259 Interrupt chip or some other interrupt port.

## **RESTART INTERRUPTS**

These three inputs have the same timing as I NTR except they cause an internal RESTART to be automatically inserted.

RST 7.5 – (Pin 7) RST 6.5 – (Pin 8) RST 5.5 - (Pin 9)

TRAP (Input)- (Pin 6)

Trap interrupt is a nonmaskable restart interrupt. It is recognized at the same time as INTR.it is unaffected by any mask or Interrupt Enable. It has the highest priority of any interrupt.

## Serial I/O Control (Pin 4 & Pin 5)

- SID (Serial input data) line -The data on this line is loaded into accumulator bit 7 whenever a RIM instruction is executed.

- SOD (Serial output data) line. The output SOD is set or reset as specified by the SIM instruction.

## Address bus (A8 –A15) - (Pin 21- Pin 28)

The address bus has 8 signal lines A8 –A15, which are unidirectional (ie) numbers only sent from microprocessor to memory, not other way.

## Address/ Data bus (AD0 - AD7)- (Pin 12- Pin 19)

It is Bi-directional. The bits AD0 –AD7are bi-directional and serve as A0 –A7and D0 –D7at the same time.

## Vcc (Pin 40)

$\blacktriangleright$  +5 volt supply.

#### Vss (Pin 20)

➢ Ground Reference.

\_\_\_\_\_

#### 3. Explain the 8085 interrupt system in detail. (May/June 2016) (May/June 2017)

An interrupt is considered to be an emergency signal. When the Microprocessor receives an interrupt signal, it suspends the currently executing program and jumps to an interrupt Service Routine (ISR) to respond to the incoming interrupt.

#### **4.1 HARDWARE INTERRUPTS**

The Hardware Interrupts of 8085 are given below:

## TRAP

RST7.5 RST6.5, RST5.5 INTR

- TRAP: TRAP has highest priority .It is non maskable edge and level triggered interrupt. TRAP has the highest priority and vectors interrupt. Edge and level triggered means that the TRAP must go high and remain high until it is acknowledged. In case of sudden power failure, it executes a ISR and send the data from main memory to backup memory. As we know that TRAP cannot be masked but it can be delayed using HOLD signal. This interrupt transfers the microprocessor's control to location 0024H.TRAP interrupts can only be masked by resetting the microprocessor. There is no other way to mask it.

- RST7.5:-It has the second highest priority. It is maskable and edge triggered interrupt. The vector address of this interrupt is 003CH.Edge sensitive means input goes high and no need to maintain high state until it is recognized. It can also be reset or masked by resetting microprocessor. It can also be reset by DI instruction.

- RST6.5 and RST5.5:-These are level triggered and maskable interrupts. When RST6.5 pin is at logic 1, INTE flip-flop is set. RST 6.5 has third highest priority and RST 5.5 has fourth highest priority. It can be masked by giving DI and SIM instructions or by resetting microprocessor.

- > **INTR:-**It is **level triggered** and **maskable** interrupt. It has the **lowest priority**. It can be disabled by resetting the microprocessor or by DI and SIM instruction.

- > **INTA** is not an interrupt. INTA is used by the Microprocessor for sending the acknowledgement.

- The vectored address of the interrupts are given in the below table. INTR is a non-vectored interrupt

| INTERRUPT | VECTORED ADDRESS |                |  |  |

|-----------|------------------|----------------|--|--|

| RST 7.5   | 003C H           | (7.5 x 0008 H) |  |  |

| RST 6.5   | 0034 H           | (6.5 x 0008 H) |  |  |

| RST 5.5   | 002C H           | (5.5 x 0008 H) |  |  |

| TRAP      | 0024 H           | (4.5 x 0008 H) |  |  |

## **<u>SIM and RIM instructions for interrupts:</u>**

- The 8085 provide additional masking facility for RST 7.5, RST 6.5 and RST 5.5 using SIM instruction.

- > The status of these interrupts can be read by executing RIM instruction.

- The masking or unmasking of RST 7.5, RST 6.5 and RST 5.5 interrupts can be performed by moving an 8-bit data to accumulator and then executing SIM instruction.

- > The format of the 8-bit data is shown below.

#### **Summary of Hardware interrupts**

| Interrup t type | Trigger        | Priority        | Maskab le | Vector<br>address |

|-----------------|----------------|-----------------|-----------|-------------------|

| TRAP            | Edge and Level | 1 <sup>st</sup> | No        | 0024H             |

| RST 7.5         | Edge           | $2^{nd}$        | Yes       | 003CH             |

| RST 6.5         | Level          | 3 <sup>rd</sup> | Yes       | 0034H             |

| RST 5.5         | Level          | $4^{th}$        | Yes       | 002CH             |

| INTR            | Level          | 5 <sup>th</sup> | Yes       | -                 |

## **4.2 SOFTWARE INTERRUPTS**

A software interrupts is a particular instructions that can be inserted into the desired location in the program. There are eight software interrupts in 8085 Microprocessor. From RST0 to RST7.

RST0 RST1 RST2 RST3 RST4 RST5 RST6 RST7

they allow the microprocessor to transfer program control from the main program to the subroutine program. After completing the subroutine program, the program control returns back to the main program.

We can calculate the vector address of these interrupts using the formula given below:

### Vector Address = Interrupt Number \* 8

So we can find simply vector address. For Example:

| RST2: | vector address=2*8 | = 16 |

|-------|--------------------|------|

| RST1: | vector address=1*8 | = 08 |

| RST3: | vector address=3*8 | = 24 |

# 4. Explain the memory organization & data transfer concepts of 8085 (May /June 2017)

## **5.1. MEMORY**

Memory in a microprocessor system is where information (data and instructions) is kept. It can be classified into two main types:

Main memory (RAM and ROM)

Storage memory (Disks, CD ROMs, etc.)

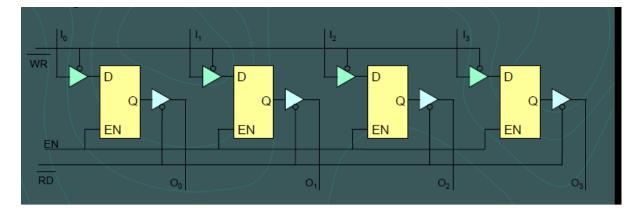

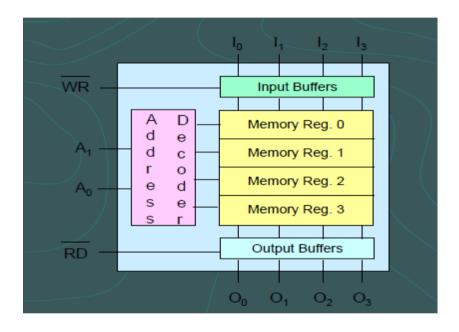

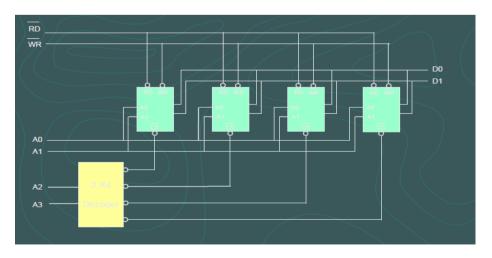

> The simple view of RAM is that it is made up of registers that are made up of flip-flops (or memory elements). The number of flip-flops in a "memory register" determines the size of the memory word.

$\succ$  ROM on the other hand uses diodes, instead of the flip-flops to permanently hold the information.

## 5.2. ACCESSING INFORMATION IN MEMORY

For the microprocessor to access (read or write) information in memory (RAM or ROM), it needs to do the following:

- 1. Select the right memory chip (using part of the address bus).

- 2. Identify the memory location (using the rest of the address bus).

- 3. Access the data (using the data bus).

## 5.3 MEMORY ORGANIZATION OF 8085

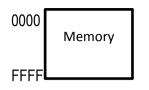

The 8085 has 16 address lines. The memory capacity of 8085 is given as

## $2^{16} = 64$ K

> Then it will need 1 memory chip with 64 k locations, or 2 chips with 32 K in each, or 4 with 16 K each or 16 of the 4 K chips, etc.

## Memory Map

$\succ$  The memory map is a picture representation of the address range and shows where the different memory chips are located within the address range.

> The 8085 has16 address lines. So, it can address a total of 64K memory locations.  $(2^{16} = 64K)$ .

$\succ$  The address range of 8085 is 0000 H- FFFF H. The memory map of 8085 is shown below

<u>Chip Select:</u> Usually, each memory chip has a CS (Chip Select) input. The chip will only work if an active signal is applied on that input.

To allow the use of multiple chips in the make up of memory, we need to use a number of the address lines for the purpose of "chip selection".

> These address lines are decoded to generate the  $2^n$  necessary CS inputs for the memory chips to be used.

- The 8085 has16 address lines. So, it can address a total of 64K memory locations.

- For the second s

- The 1K memory chip needs 10 address lines to uniquely identify the 1K locations.

$(\log_2 1024 = 10).$

That leaves 6 address lines which is the exact number needed for selecting between the 64 different chips ( $\log_2 64=6$ ).

## **Example**

## Build a memory system made up of 4 of the 4 X 4 memory chips.

If we take **four latches** and connect them together, we would have a 4-bit memory register. The 4 bit register is shown below

We will need to use 2 inputs and a decoder to identify which chip will be used at what time. This is shown in figure.

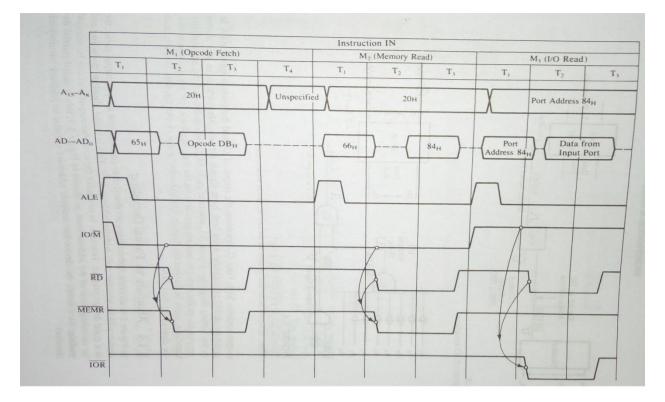

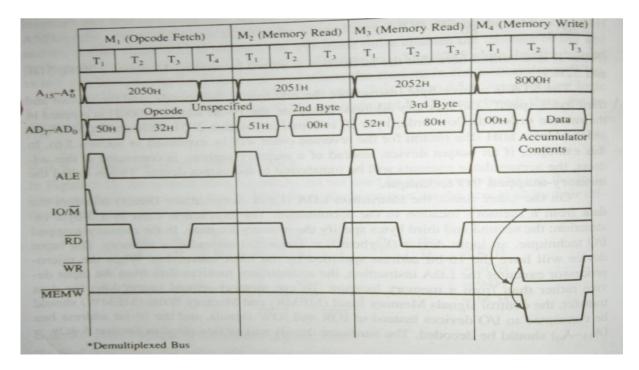

## 5. Draw the timing diagrams for the following operations

(i) Instruction Fetch (ii) Memory Read (iii) Memory Write (iv) MVI A, 32 H (v) STA 8000 (vi) IN

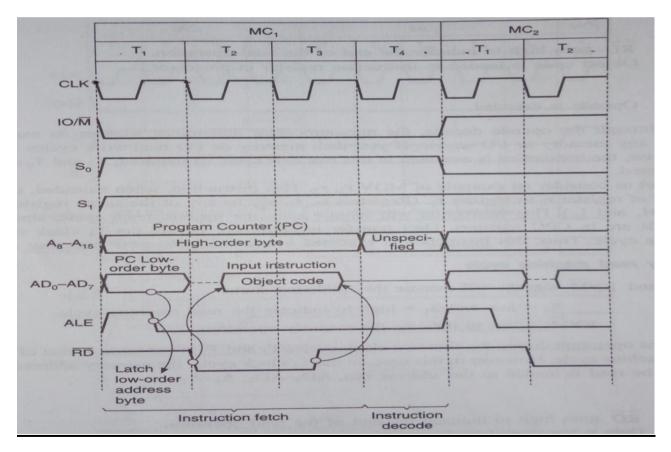

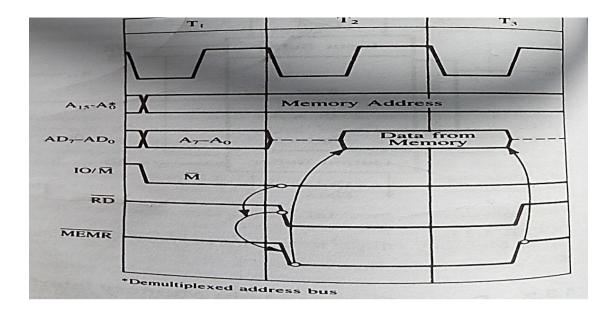

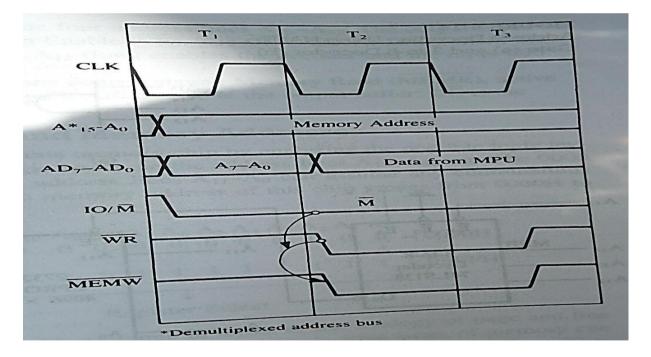

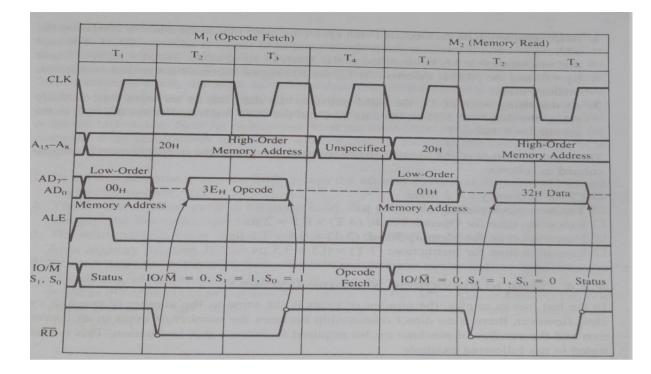

Representation of Various Control signals generated during Execution of an Instruction. Following Buses and Control Signals must be shown in a Timing Diagram:

> Higher Order Address Bus. Lower Address/Data bus ALE READ WRITE IO/M

## **Timing Diagram 1**

## **Instruction Fetch machine cycle**

**<u>Timind Diagram 2</u>**

## Memory Read

**<u>Timing Diagram 3</u>**

**Memory Write**

## **Timing Diagram 4**

## <u>MVI A, 32 H</u>

## **<u>Timing Diagram 5</u>**

## <u>STA 8000</u>

| Γ          | M <sub>1</sub> (Opcode Fetch) |                            |                                | M2 (Memory Read) |                | M <sub>3</sub> (Memory Read) |                |                | M <sub>4</sub> (Memory Write) |                           |                  |                         |                |

|------------|-------------------------------|----------------------------|--------------------------------|------------------|----------------|------------------------------|----------------|----------------|-------------------------------|---------------------------|------------------|-------------------------|----------------|

|            | <b>T</b> <sub>1</sub>         | T <sub>2</sub>             | <b>T</b> <sub>3</sub>          | T <sub>4</sub>   | T <sub>1</sub> | T <sub>2</sub>               | T <sub>3</sub> | T <sub>1</sub> | T <sub>2</sub>                | T <sub>3</sub>            | . T <sub>1</sub> | T <sub>2</sub>          | T <sub>3</sub> |

| A15-A0     |                               | 20501                      | н                              | T                | Y              | 2051H                        | as sin         | X              | 2052н                         |                           | X                | 8000H                   |                |

| AD7-AD0    | 50н                           |                            | ocode<br>32н                   | Unspec           | ified<br>51H   |                              | i Byte<br>00н  | 52н            |                               | Byte<br>OH                | - (00н           | }-{D<br>Accun<br>Conter |                |

| IO/M<br>RD | -                             | 7                          |                                |                  |                | 2                            |                |                | 1                             |                           | 1                |                         |                |

| WR         |                               | morit<br>(Senter<br>(D/) o | ando es<br>a lense<br>antifica |                  | T POLINI       |                              |                |                | A inso                        | CLD 5<br>in a m<br>ignals |                  | Z                       |                |

|            | *Dem                          | ultiplex                   | ed Bus                         |                  |                |                              |                | and o          |                               |                           | o d b            | luoda                   | Jan 1          |

## <u>Timing Diagram 6</u> <u>IN Instruction (Three Machine cycles : Opcode fetch +Memory Read + I/O Read)</u>

7. Explain the timing diagram for STA 8000 (May/Jun 2016)

## UNIT 2

## PROGRAMMING OF 8085 PROCESSOR

## PART B

## 1. Explain the various instruction formats of 8085.

$\blacktriangleright$  An **instruction** is a command to the microprocessor to perform a given task on a specified data. Each instruction has two parts: one is task to be performed, called the **operation code** (opcode), and the second is the data to be operated on, called the **operand**.

The operand (or data) can be specified in various ways. It may include 8-bit (or 16-bit ) data, an internal register, a memory location, or 8-bit (or 16-bit) address. In some instructions, the operand is implicit.

## Instruction Word Size

The 8085 instruction set is classified into the following three groups according to word size:

- 1. 1-byte instructions

2. 2-byte instructions

- **3.** 3-byte instructions

**Note:** In the 8085, "byte" and "word" are synonymous because it is an 8bit microprocessor. However, instructions are commonly referred to in terms of bytes rather than words.

#### **One-Byte Instructions**

A 1-byte instruction includes the opcode and operand in the same byte. Operand(s) are internal register and are coded into the instruction.

## **Example: MOV A,B**

#### **Two-Byte Instructions**

In a two-byte instruction, the first byte specifies the operation code and the second byte specifies the operand. Source operand is a data byte immediately following the opcode.

## Example: MVI A, 32H

## **Three-Byte Instructions**

In a three-byte instruction, the first byte specifies the opcode, and the following two bytes specify the 16-bit address. Note that the second byte is the low-order address and the third byte is the high-order address.

(opcode + data byte + data byte)

## Example: JMP 2085 H

-----

2. Explain the addressing modes of 8085 with example. ( Nov/Dec 2015 )(May/June 2017)

The various formats for specifying operands are called the ADDRESSING MODES. For 8085, they are:

- 1. Immediate addressing mode.

- 2. Register addressing mode.

- 3. Direct addressing mode.

- 4. Register Indirect (or) indirect addressing mode.

## Immediate addressing mode

Data is present in the instruction. Load the immediate data to the destination provided.

## Format: MVI R,data

## **Example:**

1. MVI A, OF H

Load OF H to register A

After execution

$(\mathbf{A}) = \mathbf{OF} \mathbf{H}$

## 2. LXI D FFF0 H

Load FFF0 H to D-E

After execution

$(\mathbf{D}) (\mathbf{E}) = \mathbf{FFF0} \mathbf{H}$

#### **Register addressing mode**

Data is provided through the registers.

Format: MOV Rd, Rs

**Example:**

MOV B, D

INX H

#### **Direct addressing mode**

Used to accept data from outside devices to store in the accumulator or send the data stored in the accumulator to the outside device.

#### **Example:**

LDA 2000 H STA 8000 H

#### **Register Indirect (or) Indirect Addressing mode**

This means that the Effective Address is calculated by the processor. And the contents of the address (and the one following) is used to form a second address. The second address is where the data is stored. Note that this requires several memory accesses; two accesses to retrieve the 16-bit address and a further access (or accesses) to retrieve the data which is to be loaded into the register.

## Example: MOV B,M

#### Move the contents of memory location addressed by register pair H-L to B

**3.** Explain the Different types of instruction in 8085. (May/Jun 2016), Explain the logical operations of 8085. (Dec 2016)

\_\_\_\_\_

An **instruction** is a binary pattern designed inside a microprocessor to perform a specific function. The entire group of instructions, called the **instruction set**,

determines what type of functions the microprocessor can perform. These instructions can be classified into following five functional categories:

- 1. Data transfer (copy) operations

- 2. Arithmetic operations

- 3. Logical operations

- 4. Branching operations

- 5. Machine-control operations

## 3.1. Data Transfer (Copy) Operations

This group of instructions copy data from a location called a source to another location called a destination, without modifying the contents of the source. In technical manuals, the term *data transfer* is used for this copying function. However, the term *transfer* is misleading; it creates the impression that the contents of the source are destroyed when, in fact, the contents are retained without any modification.

These operations transfer: Data between registers.

Data Byte to a register or memory location. Data between a memory location and a register. Data between an I\O Device and the accumulator.

The examples are listed below

## MOV, MVI, LDA, and STA

## 3.2 .Arithmetic Operations

These instructions perform arithmetic operations such as addition, subtraction, increment, and decrement.

**Addition** - Any 8-bit number, or the contents of a register or the contents of a memory location can be added to the contents of the accumulator and the sum is stored in the accumulator. No two other 8-bit registers can be added directly (e.g., the contents of register B cannot be added directly to the contents of the register C). The instruction DAD is an exception; it adds 16-bit data directly in register pairs.

## Example:

## ADD, ADI

**Subtraction -** Any 8-bit number, or the contents of a register, or the contents of a memory location can be subtracted from the contents of the accumulator and the results stored in the accumulator. The subtraction is performed in 2's complement, and the results if negative, are expressed in 2's complement. No two other registers can be subtracted directly.

## **Example:**

## SUB, SUI

**Increment/Decrement** - The 8-bit contents of a register or a memory location can be incremented or decrement by 1. Similarly, the 16-bit contents of a register pair (such as BC) can be incremented or decrement by 1. These increment and decrement operations differ from addition and subtraction in an important way; i.e., they can be performed in any one of the registers or in a memory location.

## INX Rp (Incrementthe16-bitnumberintheregisterpair)

## DCX Rp (Decrementthe16-bitnumberintheregisterpair)

## **3.3.** Logical Operations

These instructions perform various logical operations with the contents of the accumulator.

**AND, OR Exclusive-OR** - Any 8-bit number, or the contents of a register, or of a memory location can be logically AND, OR, or Exclusive-OR with the contents of the accumulator. The results are stored in the accumulator.

#### **Example:**

| ANA R/M | AND Accumulator with Reg/Mem         |

|---------|--------------------------------------|

| ANI #   | AND Accumulator With an 8-bit number |

| ORA R/M | <b>OR Accumulator with Reg/Mem</b>   |

| ORI #   | OR Accumulator With an 8-bit number  |

| XRA R/M | XOR Accumulator with Reg/Mem         |

| XRI #   | XOR Accumulator With an 8-bit number |

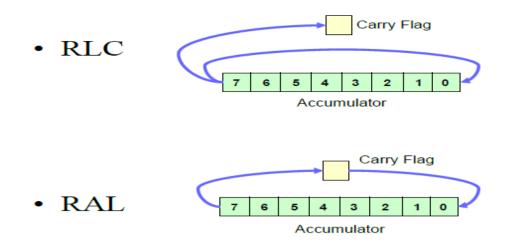

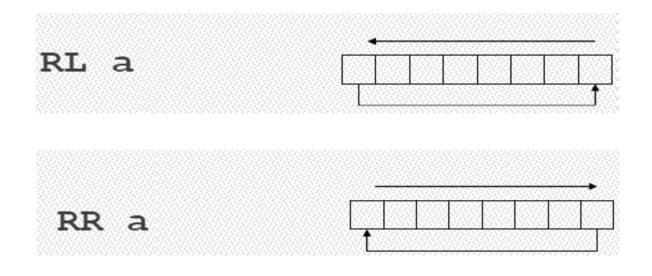

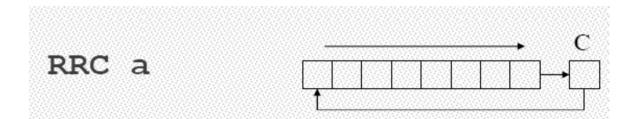

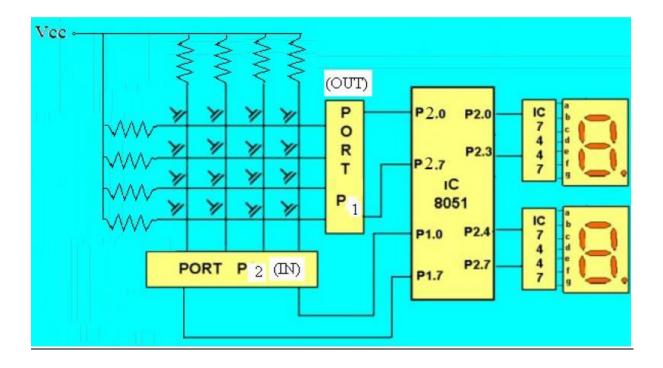

Rotate- Each bit in the accumulator can be shifted either left or right to the next position.

#### **Example:**

|       | RLC | Rotate the accumulator left. Bit 7 goes to bit 0 and the carry flag.                            |

|-------|-----|-------------------------------------------------------------------------------------------------|

|       | RAL | Rotate the accumulator left through the carry. Bit 7 goes to the carry and carry goes to bit 0. |

|       | RRC | Rotate the accumulator right. Bit 0 goes to bit 7 AND the Carry flag                            |

| carry | RAR | Rotate the accumulator right through the carry. Bit 0 goes to the                               |

| carry |     | and carry goes to bit 7.                                                                        |

**Compare**- Any 8-bit number, or the contents of a register, or a memory location can be compared for equality, greater than, or less than, with the contents of the accumulator.

#### **Example:**

#### CMP R/M Compare the contents of the register or memory location to the

Contents of the accumulator.

CPI number Compare the 8-bit number to the contents of the accumulator.

• The compare instruction sets the flags (Z, Cy, and S).

**Complement** - The contents of the accumulator can be complemented. All 0s are replaced by 1s and all 1s are replaced by 0s.

#### Example: CMA (ones complement of Accumulator (ACC) content)

## **3.4. Branching Operations**

This group of instructions alters the sequence of program execution either conditionally or unconditionally.

**Jump - Conditional jumps** are an important aspect of the decision-making process in the programming. These instructions test for a certain conditions (e.g., Zero or Carry flag) and alter the program sequence when the condition is met. In addition, the instruction set includes an instruction called *unconditional jump*.

**CALL, Return, and Restart -** These instructions change the sequence of a program either by calling a subroutine or returning from a subroutine. The conditional CALL and Return instructions also can test condition flags.

## **Unconditional Branch**

| JMP Address  | Jump to the address specified (Go to).                      |

|--------------|-------------------------------------------------------------|

| CALL Address | Jump to the address specified but treat it as a subroutine. |

| RET          | Return from a subroutine.                                   |

The addresses supplied to all branch operations must be 16-bits.

## **Conditional Branch**

Go to new location if a specified condition is met.

| JZ Address  | (Jump on Zero) Go to address specified if the Zero flag is set.                    |

|-------------|------------------------------------------------------------------------------------|

| JNZ Address | (Jump on NOT Zero) Go to address specified if the Zero flag is Not set.            |

| JC Address  | (Jump on Carry) Go to the address specified if the <b>Carry flag is Set</b> .      |

| JNC Address | (Jump on No Carry)Go to the address specified if the <b>Carry flag</b> is not set. |

| JP Address  | (Jump on Plus)Go to the address specified if the Sign flag is not set              |

| JM Address  | (Jump on Minus)Go to the address specified if the Sign flag is set.                |

## **3.5. Machine Control Operation**

These instructions control machine functions such as Halt, Interrupt, or do nothing.

HLT NOP

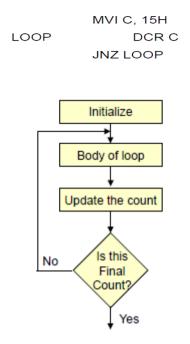

## 4. Explain the concept of loop indexing & delay loops with examples.

> A loop counter is set up by loading a register with a certain value ,then using the DCR (to decrement) and INR (to increment) the contents of the register are updated.

$\succ$  A loop is set up with a conditional jump instruction that loops back or not depending on whether the count has reached the termination count.

#### **Sample ALP and Flowchart**

#### **DELAY LOOP**

We can use a loop to produce a certain amount of time delay in a program. The example ALP is given below

The T-states for the above ALP is

| MVI C, FFH | 7 T-States  |

|------------|-------------|

| LOOP DCR C | 4 T-States  |

| JNZ LOOP   | 10 T-States |

The **first instruction** initializes the loop counter and is executed only once requiring only **7 T-States**.(Refer the Timing Diagram of MVI A, 32 H)

The following **two instructions** form a loop that requires **14 T-States** to execute and is repeated **255**(Decimal value of FF H) times until C becomes 0.

We need to keep in mind though that in the last iteration of the loop, the JNZ instruction will fail and require only 7 T-States rather than the 10.

Therefore, we must **deduct 3 T-States** from the total delay to get an accurate delay calculation.

> To calculate the delay, we use the following formula:

Here, TO= 7 T-States

TL= (14 X 255) -3 = 3567 T-States14 T-States for the 2 instructions repeated 255 times (**FF<sub>H</sub> = 255**<sub>10</sub>) reduced by the 3 T-States for the final JNZ.

## **NESTED DELAY LOOP**

A nested loop structure can be used to increase the total delay produced. Here, more than one loop is used

#### Sample Program –Nested delay loop

MVI B, 10H LOOP2 MVI C, FFH LOOP1 DCR C JNZ LOOP1 DCR B JNZ LOOP2

5. What is meant by subroutine? Explain how the stack is affected while calling subroutine program. (May/ June 2017)

- ➤ A subroutine is a group of instructions

- That is used repeatedly in different places of the program.

- Rather than repeat the same instructions several times.

- It can be grouped into a subroutine and call from the different locations.

- Instructions for dealing with subroutines.

- The **CALL** instruction is used to redirect program execution to the subroutine.

- The **RET** instruction is used to return the execution to the calling routine.

Set the SP correctly before using CALL

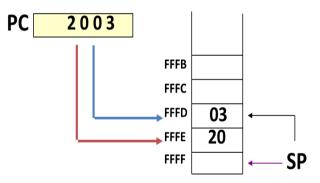

## FOR CALL INSTRUCTION

## Example

### **Instruction: CALL 5000 H**

#### Assume that the CALL instruction is in the address 2000

2000 CALL 5000 2003

The Process can explained as

- Push the PC value onto the stack

- Load PC with 16-bit address supplied CALL instruction

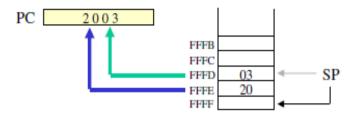

## FOR RET INSTRUCTION

The Process Is

- ➤ Load PC with stack top

- $\succ$  POP PC

## **Conditional CALL and RETURN Instructions**

The 8085 supports conditional CALL and conditional RETURN instructions. The same conditions used with conditional JUMP instructions can be used.

CC, call subroutine if Carry flag is set.

CNC, call subroutine if Carry flag is not set

**RC**, return from subroutine if Carry flag is set

**RNC**, return from subroutine if Carry flag is not set

## PASSING DATA TO A SUBROUTINE

Data is passed to a subroutine through registers.

## **Call by Reference:**

The data is stored in one of the registers by the calling program and the subroutine uses the value from the register. The register values get modified within the subroutine. Then these modifications will be transferred back to the calling program upon returning from a subroutine

## **Call by Value:**

The data is stored in one of the registers, but the subroutine first PUSHES register values in the stack and after using the registers, it POPS the previous values of the registers from the stack while exiting the subroutine. i.e. the original values are restored before execution returns to the calling program.

## **A PROPER SUBROUTINE**

> According to Software Engineering practices, a proper subroutine:

- Is only entered with a CALL and exited with an RTE

- Has a single entry point

- > Do not use a CALL statement to jump into different points of the same subroutine.

- Has a single exit point

- > There should be one return statement from any subroutine.

\_\_\_\_\_

#### 6. 8085 programs

(i) Write a ALP to multiply two numbers (Dec 2016)

#### Flowchart to multiply two number

## PROGRAM

| LDA 2000                                | // Load multiplicant to accumulator             |  |

|-----------------------------------------|-------------------------------------------------|--|

| MOV B, A                                | // Move multiplicant from A (acc) to B register |  |

| LDA 2001                                | // Load multiplier to accumulator               |  |

| MOV C, A                                | // Move multiplier from A to C                  |  |

| MVI A, 00                               | // Load immediate value 00 to a                 |  |

| Loop: ADD B // Add B(multiplier) with A |                                                 |  |

| DCR C                                   | // Decrement C, it act as a counter             |  |

| JNZ Loop                                | // Jump to L if C reaches 0                     |  |

STA2010// Store result in to memoryHLT// End

| (ii) . Write a 8085 program to convert a Hexadecimal number to ASCII code (Dec 2016). |                                       |  |

|---------------------------------------------------------------------------------------|---------------------------------------|--|

| LDA 5000                                                                              | //Get Hexa Data                       |  |

| MOV B,A                                                                               |                                       |  |

| ANI 0F                                                                                | // Mask Upper Nibble                  |  |

| CALL SUE                                                                              | 31 //Get ASCII code for upper nibble  |  |

| STA 5001                                                                              |                                       |  |

| MOV A,B                                                                               |                                       |  |

| ANI F0                                                                                | // Mask Lower Nibble                  |  |

| RLC                                                                                   |                                       |  |

| CALL SUE                                                                              | 31 // Get ASCII code for lower nibble |  |

| STA 5002                                                                              |                                       |  |

| HLT                                                                                   | // Halt the program.                  |  |

SUB1: CPI 0A

JC SKIP

ADI 07

SKIP: ADI 30

RET // Return Subroutine

## **RESULT**

Input:

Data 1: HEX data - E4H in memory location 5000

Output:

Data 1: 34H in memory location 5001(ASCII Code for 4)

Data 2: 45H in memory location 5002(ASCII Code for E)

\_\_\_\_\_

## (iii) Write a ALP to arrange n numbers in ascending order (May/Jun 2016)

| LXI H,5000 // Set pointer for array<br>MOV C,M // Load the Count |  |  |  |

|------------------------------------------------------------------|--|--|--|

| DCR C // Decrement Count                                         |  |  |  |

| REPEAT: MOV D,C                                                  |  |  |  |

| LXI H,5001                                                       |  |  |  |

| LOOP: MOV A,M // copy content of memory location to Accumulator  |  |  |  |

| INX H                                                            |  |  |  |

| CMP M                                                            |  |  |  |

| JC SKIP // jump to skip if carry generated                       |  |  |  |

| MOV B,M // copy content of memory location to B - Register       |  |  |  |

| MOV M,A // copy content of Accumulator to memory location        |  |  |  |

| DCX H // Decrement content of HL pair of registers               |  |  |  |

| MOV M,B // copy content of B - Register to memory location       |  |  |  |

| INX H // Increment content of HL pair of registers               |  |  |  |

| SKIP: DCR D // Decrement content of Register - D                 |  |  |  |

| JNZ LOOP // jump to loop if not equal to zero                    |  |  |  |

| DCR C // Decrement count                                         |  |  |  |

| JNZ REPEAT // jump to repeat if not equal to zero                |  |  |  |

| HLT // Terminate Program                                         |  |  |  |

## (iv) Write a program to output square wave 1 kHz frequency on the SOD pin of 8085 for 5 seconds. (May/Jun 2016).

| LXI SP, 27FFH<br>LXI B, 1388H | <ul><li>// Initialize stack pointer</li><li>// Initialize counter with count 5000.</li></ul> |

|-------------------------------|----------------------------------------------------------------------------------------------|

| BACK: MVI A, COH              |                                                                                              |

| SIM                           | // Send high on SOD pin                                                                      |

| CALL DELAY                    | // Wait for 0.5 msec                                                                         |

| MVI A, 40H                    | // Send low on SOD pin                                                                       |

| CALL DELAY                    | // wait for. 5 msec                                                                          |

| DCX B                         | // Decrement count by 1                                                                      |

| MOV A, C                      |                                                                                              |

| ORA B                         | // Check if $count = 0$                                                                      |

| JNZ BACK                      | // If not, repeat                                                                            |

| HLT                           | // Stop program execution                                                                    |

|                               |                                                                                              |

Delay subroutine:

Delay: LXI D, Count Back: DCX D MOV A, D ORA E JNZ Back RET

# (V) Write an 8085 assembly language program to divide an 8 bit number by another 8 bit number (May/June 2017)

## **ALGORITHM:**

- 1) Start the program by loading HL register pair with address of memory location.

- 2) Move the data to a register (B register).

- 3) Get the second data and load into Accumulator.

- 4) Compare the two numbers to check for carry.

- 5) Subtract the two numbers.

- 6) Increment the value of carry.

- 7) Check whether repeated subtraction is over and store the value of product and carry in memory location.

- 8) Terminate the program.

## **PROGRAM:**

|       | LXI H, 4150<br>MOV B,M<br>MVI C,00<br>INX H | Get the dividend in B – reg.<br>Clear C – reg for qoutient                               |

|-------|---------------------------------------------|------------------------------------------------------------------------------------------|

| NEXT: | MOV A,M<br>CMP B<br>JC LOOP                 | Get the divisor in A – reg.<br>Compare A - reg with register B.<br>Jump on carry to LOOP |

|       | SUB B<br>INR C                              | Subtract A – reg from B- reg.<br>Increment content of register C.                        |

| LOOP: | JMP NEXT<br>STA 4152<br>MOV A,C             | Jump to NEXT<br>Store the remainder in Memory                                            |

|       | STA 4153<br>HLT                             | Store the quotient in memory Terminate the program.                                      |

## **RESULT:**

Input:

| F ( | 4150)  |

|-----|--------|

| FF  | (4251) |

Output:

01 (4152) ---- Remainder FE (4153) ---- Quotient

(VI) Write an 8085 ALP to find the largest among N numbers [May/June 2017].

#### **ALGORITHM:**

- 1) Load the address of the first element of the array in HL pair

- 2) Move the count to B reg.

- 3) Increment the pointer

- 4) Get the first data in A reg.

- 5) Decrement the count.

- 6) Increment the pointer

- 7) Compare the content of memory addressed by HL pair with that of A reg.

- 8) If Carry = 0, go to step 10 or if Carry = 1 go to step 9

- 9) Move the content of memory addressed by HL to A reg.

- 10) Decrement the count

- 11) Check for Zero of the count. If ZF = 0, go to step 6, or if ZF = 1 go to next step.

- 12) Store the largest data in memory.

- 13) Terminate the program.

#### **PROGRAM:**

LXI H, 4200 Set pointer for array MOV B, M Load the Count INX H Set 1st element as largest data MOV A, M DCR B Decrements the count LOOP: INX H CMP M f A - reg > M go to AHEADJNC AHEAD MOVA, M Set the new value as largest AHEAD: DCR B JNZ LOOP Repeat comparisons till count = 0Store the largest value at 4300 STA 4300 HLT

HLI

#### **RESULTS:**

Input: 05 (4200) Array Size

Output: 0A (4201) F1 (4202) 1F (4203) 26 (4204) FE (4205) FE (4300)

## UNIT 3 - 8051 MICRO CONTROLLER PART B

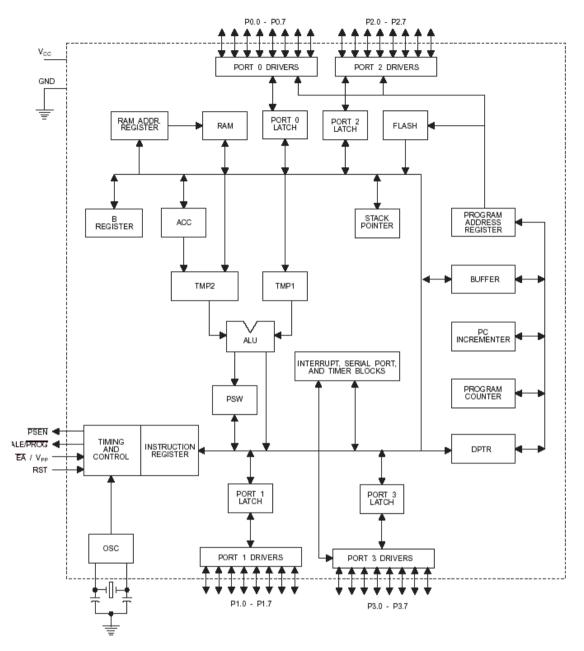

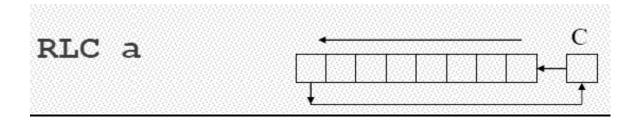

# 1. Describe the architecture of 8051 with neat diagram. (May/Jun 2016, Nov/Dec 2015)(May/June 2017)

The 8051 is a Harvard architecture (separate instruction/data memories) MCS-51 family of single chip microcontroller developed by Intel. This is mostly used microcontroller in the robotics, home appliances like mp3 player, washing machines, electronic iron and industries. The block diagram is given below

## <u>ALU</u>

Arithmetic Logical Unit .This unit is used for the arithmetic calculations.

## **A-ACCUMULATOR**

This register is used for arithmetic operations. This is also bit addressable and 8 bit register.

#### **B-REGISTER**

This register is used in only two instructions MUL AB and DIV AB. This is also bit addressable and 8 bit register.

## PC-PROGRAM COUNTER

PC Points to the address of next instruction to be executed from ROM .It is 16 bit register means the 8051 can access program address from 0000H to FFFFH.

## 8051 FLAG BITS AND PSW REGISTER

Flag register in 8051 is called as program status word (PSW). This special function register PSW is also bit addressable and 8 bit wide means each bit can be set or reset independently.

| PSW0.7 | PSW0.6 | PSW0.5 | PSW0.4 | PSW0.3 | PSW0.2 | PSW0.1 | PSW0.0 |

|--------|--------|--------|--------|--------|--------|--------|--------|

| CY     | AC     | F0     | RS1    | RS0    | ov     |        | Ρ      |

There are four flags in 8051

$\mathbf{P} \rightarrow \mathbf{Parity} \ \mathbf{flag} \rightarrow \mathrm{PSW} \ 0.0$ 1 - odd number of 1 in ACC

0 – even number of 1 in ACC

**OV** (**PSW 0.2**)  $\rightarrow$  **overflow flag**  $\rightarrow$  this is used to detect error in signed arithmetic operation. This is similar to carry flag but difference is only that carry flag is used for unsigned operation.

#### RS1 (PSW0.4) & RS0 (PSW0.3) Register Bank Select

0 0 Bank 0

- 01 Bank 1

- 1 0 Bank 2

- 1 1 Bank 3

for selecting Bank 1, we use following commands

SETB PSW0.3 (means RS0=1) CLR PSW0.4 (means RS1=0) Initially by default always Bank 0 is selected.

$F0 \rightarrow$  user definable bit

$AC \rightarrow Auxiliary carry flag \rightarrow$  when carry is generated from D3 to D4, it is set to 1.

$CY \rightarrow carry flag \rightarrow Affected after 8 bit addition and subtraction. It is used to detect error in unsigned arithmetic operation. We can also use it as single bit storage.$

SETB C  $\rightarrow$  for cy = 1

CLR C  $\rightarrow$  for cy = 0

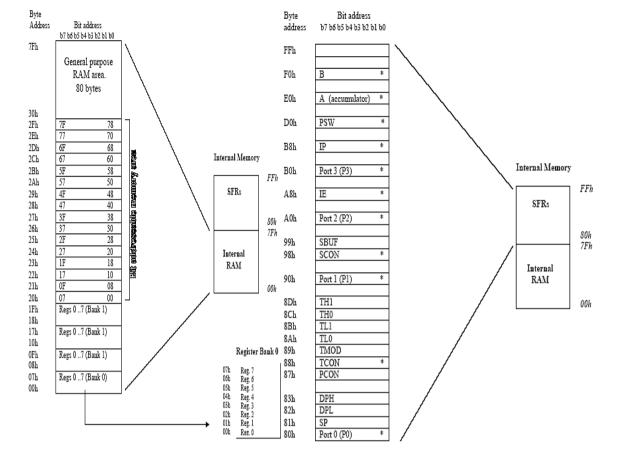

## RAM /Data memory (128 Byte)

The 8051 has 128 byte Random Access memory for data storage RAM consists of the register banks, stack for temporary data storage. It also consists of some special function register (SFR) which are used for some specific purpose like timer, input output ports etc. Normally microcontroller has 256 byte RAM in which 128 byte is used for user space which is normally Register banks and stack. But other 128 byte RAM which consists of SFRs.

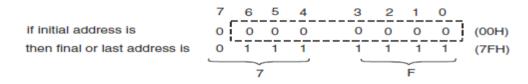

$\blacktriangleright$  We know that 128 byte = 2<sup>7</sup> byte

Since 27 bytes so last 7 bits can be changed so total locations are from 00H to 7F H. This procedure of calculating the memory address is called as "memory mapping". We can save data on memory locations from 00H to 7FH.

#### ROM (4KB)

- ▶ In 8051, 4KB read only memory (ROM) is available for program storage.

- The total 4KB locations are available from 0000H to 0FFFH. At which we can save the program.

#### TIMERS AND COUNTERS

Timer means which can give the delay of particular time between some events. This delay can be provided through some assembly program but in microcontroller two hardware pins are available for delay generation. These hardware pins can be also used for counting some external events.

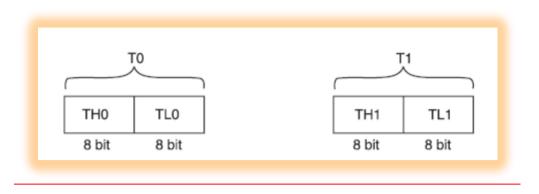

In8051, two timer pins are available T0 and T1, by these timers we can give the delay of particular time if we use these in timer mode. Two special function registers are available.

#### **STACK POINTER (SP)**

SP is a 8bit register. It indicates current RAM address available for stack or it points the top of stack. The SP is Initially by default at 07H because first location of stack is 08H.

- After each PUSH instruction the SP is incremented by one after PUSH instruction SP is decremented.

- After each POP instruction the SP is decremented.

## **DPTR (DATA POINTER)**

DPTR is a 16 bit register; it is divided into two parts DPH and DPL.

- $\rightarrow$  DPH for Higher order 8 bits, DPL for lower order 8 bits.

- $\rightarrow$  DPTR, DPH, DPL these all are SFR ) s in 8051.

## SERIAL PORT

There are two pins available for serial communication TXD and RXD.

- > Normally TXD is used for transmitting serial data which is in SBUF register.

- > RXD is used for receiving the serial data.

- > SCON register is used for controlling the operation.

## **INPUT OUTPUT PORTS (I/O PORTS)**

> There are four input output ports available P0, P1, P2, P3.

- Each port is 8 bit wide and has special function register P0, P1, P2, P3.which are bit addressable means each bit can be set or reset by the Bit instructions (SETB for high, CLR for low) independently.

- The port 0 can perform dual works. It is also used as Lower order address bus (A0 to A7) multiplexed with 8 bit data bus P0.0 to P0.7 is AD0 to AD7 respectively the address bus and data bus is demultiplex by the ALE signal and latch which is further discussed in details.

- > Port 2 can be used as I/O port as well as higher order address bus A8 toA15.

- Port 3 also have dual functions it can be worked as I/O as well as each pin of P3 has specific function.

- P3.0 RXD Serial I / P for Asynchronous communication Serial O / P for Synchronous communication.

- P3.1 TXD Serial data transmit.

- P3.2 INT0 External Interrupt 0.

- P3.3 INT1 External Interrupt 1.

- P3.4 T0 Clock input for counter 0.

- P3.5 T1 Clock input for counter 1.

- P3.6 WR Signal for writing to external memory.

- P3.7 RD Signal for reading from external memory.

When external memory is interfaced with 8051 then P0 and P2 can't be worked as I/O port they works as address bus and data bus, otherwise they can be accessed as I/O ports.

## **OSCILLATOR**

It is used for providing the clock to MC8051 which decides the speed or baud rate of MC. We use crystal which frequency varies from 4MHz to 30 MHz; normally we use 11.0592 MHz frequency.

## **INTERRUPTS**

Interrupts are defined as requests because they can be refused (masked) if they are not used, that is when an interrupt is acknowledged. A special set of events or routines are followed to handle the interrupts. These special routines are known as interrupt handler or interrupt service routines (ISR). These are located at a special location in memory.

> INT0 and INT1 are the pins for external interrupts.

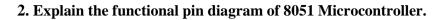

- **≻** <u>Vcc (pin 40</u>) :

- Vcc provides supply voltage to the chip.

- $\succ$  The voltage source is +5V.

- Solution (pin 20) : ground

- XTAL1 and XTAL2 (pins 19,18) :

- ➤ These 2 pins provide external clock.

- ▶ Way 1 : using a quartz crystal oscillator

- ➤ Way 2 : using a TTL oscillator

## > <u>RST (PIN 9) : RESET</u>

- ▶ It is an input pin and is active high (normally low).

- > The high pulse must be high at least 2 machine cycles.

- ➢ It is a power-on reset.

- Upon applying a high pulse to RST, the microcontroller will reset and all values in registers will be lost.

- Reset values of some 8051 registers.

## > <u>/EA (PIN 31) : EXTERNAL ACCESS</u>

- > The /EA pin is connected to GND to indicate the code is stored externally.

- > /PSEN & ALE are used for external ROM.

- ➤ For 8051, /EA pin is connected to Vcc (5 V).

- ➤ "/" means active low.

## > <u>/PSEN (PIN 29) : PROGRAM STORE ENABLE</u>

> This is an output pin and is connected to the OE pin of the ROM.

## > <u>ALE (PIN 30) : ADDRESS LATCH ENABLE</u>

- ▶ It is an output pin and is active high.

- $\blacktriangleright$  8051 port 0 provides both address and data.

- > The ALE pin is used for de-multiplexing the address and data .

## > <u>I/O PORT PINS</u>

- ➤ The four ports P0, P1, P2, and P3.

- ➤ Each port uses 8 pins.

- ➤ All I/O pins are bi-directional.

\_\_\_\_\_

## 3. Explain the ROM and RAM structure of 8051 (Dec 2016).

The 8051 microcontroller's memory is divided into Program Memory and Data Memory. Program Memory (ROM) is used for permanent saving program being executed, while Data Memory (RAM) is used for temporarily storing and keeping intermediate results and variables.

#### 3.1PROGRAM MEMORY (ROM)

Program Memory (ROM) is used for permanent saving program (CODE) being executed. The memory is read only. Depending on the settings made in compiler, program

memory may also use to store a constant data. The 8051 executes programs stored in program memory only. Code memory type specified is used to refer to program memory.

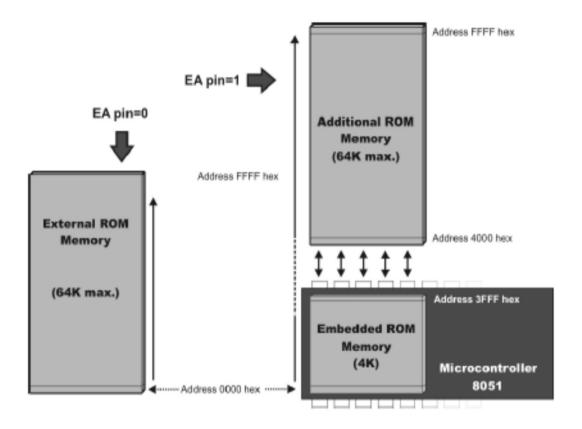

8051 memory organization alows external program memory to be added. How does the microcontroller handle external memory depends on the pin EA logical state. This is shown in the following figure.

## **3.2. INTERNAL DATA MEMORY (RAM)**

Up to 256 bytes of internal data memory are available depending on the 8051 derivative. Locations available to the user occupy addressing space from 0 to 7Fh, i.e.

First 128 registers and this part of RAM is divided in several blocks. The first 128 bytes of internal data memory are both directly and indirectly addressable. The upper 128 bytes of data memory (from 0x80 to 0xFF) can be addressed only indirectly.

Since internal data memory is used for CALL stack also and there is only 256 bytes splited over few different memory areas fine utilizing of this memory is crucial for fast and compact code.

Memory block in the range of 20h to 2Fh is bit addressable, which means that each bit being there has its own address from 0 to 7Fh. Since there are 16 such registers, this block contains in total of 128 bits with separate addresses (Bit 0 of byte 20h has the bit address 0, and bit 7 of byte 2Fh has the bit address 7Fh).

#### **RAM MEMORY MAP**

Byte address

#### **8051 INTERNAL RAM PARTITIONING & SFR**

#### EXTERNAL DATA MEMORY

Access to external memory is slower than access to internal data memory. There may be up to 64K Bytes of external data memory. Several 8051 devices provide on chip XRAM space that is accessed with the same instructions as the traditional external data space. This XRAM space is typically enabled via proper setting of SFR register and overlaps the external memory space. Setting of that register must be manually done in code, before any access to external memory or XRAM space is made.

#### SPECIAL FUNCTION REGISTERS (SFRS)

The 8051 provides 128 bytes of memory for SFRs. There are 21 Special function registers (SFR) in 8051 micro controller and this includes Register A, Register B, PSW, PCON etc. There are 21 unique locations for these 21 special function registers and each of these register is of 1 byte size. Some of these special function registers *are bit addressable* (which means you can access 8 individual bits inside a single byte), while some others are *only byte addressable*. The SFR are listed in the below table.

| Symbol       | Name                             | Address |

|--------------|----------------------------------|---------|

| ACC*         | Accumulator                      | 0E0H    |

| B*           | B register                       | 0F0H    |

| PSW*         | Program status word              | 0D0H    |

| SP           | Stack pointer                    | 81H     |

| DPTR         | Data pointer 2 bytes             |         |

| DPL          | Low byte                         | 82H     |

| DPH          | High byte                        | 83H     |

| <b>P</b> 0*  | Port 0                           | 80H     |

| P1*          | Port 1                           | 90H     |

| P2*          | Port 2                           | 0A0H    |

| P3*          | Port 3                           | OBOH    |

| IP*          | Interrupt priority control       | 0B8H    |

| IE*          | Interrupt enable control         | 0A8H    |

| TMOD         | Timer/counter mode control       | 89H     |

| TCON*        | Timer/counter control            | 88H     |

| T2CON*       | Timer/counter 2 control          | 0C8H    |

| T2MOD        | Timer/counter mode control       | 0C9H    |

| THO          | Timer/counter 0 high byte        | 8CH     |

| TL0          | Timer/counter 0 low byte         | 8AH     |

| TH1          | Timer/counter 1 high byte        | 8DH     |

| TL1          | Timer/counter 1 low byte         | 8BH     |

| TH2          | Timer/counter 2 high byte        | 0CDH    |

| TL2          | Timer/counter 2 low byte         | 0CCH    |

| RCAP2H       | T/C 2 capture register high byte | 0CBH    |

| RCAP2L       | T/C 2 capture register low byte  | 0CAH    |

| SCON*        | Serial control                   | 98H     |

| SBUF         | Serial data buffer               | 99H     |

| PCON         | Power control                    | 87H     |

| * Bit-addres | sable                            |         |

## 4. Explain the I/O ports and data transfer concepts of 8051. (Dec 2016)

- > There are four input output ports available **P0**, **P1**, **P2**, **P3**.

- Each port is 8 bit wide and has special function register P0, P1, P2, P3.which are bit addressable means each bit can be set or reset by the Bit instructions (SETB for high, CLR for low) independently.

- The port 0 can perform dual works. It is also used as Lower order address bus (A0 to A7) multiplexed with 8 bit data bus P0.0 to P0.7 is AD0 to AD7 respectively the address bus and data bus is de-multiplex by the ALE signal and latch which is further discussed in details.

- > Port 2 can be used as I/O port as well as higher order address bus A8 toA15.

- Port 3 also have dual functions it can be worked as I/O as well as each pin of P3 has specific function.

- P3.0 RXD Serial I / P for Asynchronous communication Serial O / P for Synchronous communication.

- P3.1 TXD Serial data transmit.

- P3.2 INTO External Interrupt 0.

- P3.3 INT1 External Interrupt 1.

- P3.4 T0 Clock input for counter 0.

- P3.5 T1 Clock input for counter 1.

- P3.6 WR Signal for writing to external memory.

- P3.7 RD Signal for reading from external memory.

When external memory is interfaced with 8051 then P0 and P2 can't be worked as I/O port they works as address bus and data bus, otherwise they can be accessed as I/O ports. The port addresses are listed in the below table.

| <u>P0</u>   | Addr | P1   | Addr | P2   | Addr | P3   | Addr | Port's Bit |

|-------------|------|------|------|------|------|------|------|------------|

| P0.0        | 80   | P1.0 | 90   | P2.0 | A0   | P3.0 | B0   | D0         |

| <b>P0.1</b> | 81   | P1.1 | 91   | P2.1 | A1   | P3.1 | B1   | D1         |

| P0.2        | 82   | P1.2 | 92   | P2.2 | A2   | P3.2 | B2   | D2         |

| P0.3        | 83   | P1.3 | 93   | P2.3 | A3   | P3.3 | B3   | D3         |

| P0.4        | 84   | P1.4 | 94   | P2.4 | A4   | P3.4 | B4   | D4         |

| P0.5        | 85   | P1.5 | 95   | P2.5 | A5   | P3.5 | B5   | D5         |

| P0.6        | 86   | P1.6 | 96   | P2.6 | A6   | P3.6 | B6   | D6         |

| P0.7        | 87   | P1.7 | 97   | P2.7 | A7   | P3.7 | B7   | D7         |

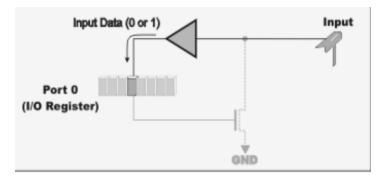

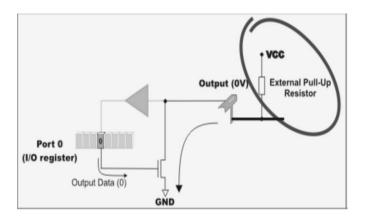

#### PORT 0

The P0 port is characterized by two functions. If external memory is used then the lower address byte (addresses A0-A7) is applied on it. Otherwise, all bits of this port are configured as inputs/outputs. The other function is expressed when it is configured as an output. Unlike other ports consisting of pins with built-in pull-up resistor connected by its end to 5 V power supply, pins of this port have this resistor left out. This apparently small difference has its consequences:

If any pin of this port is configured as an input then it acts as if it "floats". Such an input has unlimited input resistance and in determined potential.

When the pin is configured as an output, it acts as an "open drain". By applying logic 0 to a port bit, the appropriate pin will be connected to ground (0V). By applying logic 1, the external output will keep on "floating". In order to apply logic 1 (5V) on this output pin, it is necessary to built in an external pull-up resistor.

## <u>PORT 1</u>

P1 is a true I/O port, because it doesn't have any alternative functions as is the case with P0, but can be cofigured as general I/O only. It has a pull-up resistor built-in and is completely compatible with TTL circuits.

## PORT 2

P2 acts similarly to P0 when external memory is used. Pins of this port occupy addresses intended for external memory chip. This time it is about the higher address byte with addresses A8-A15. When no memory is added, this port can be used as a general input/output port showing features similar to P1.

## <u>PORT 3</u>

All port pins can be used as general I/O, but they also have an alternative function. In order to use these alternative functions, a logic one (1) must be applied to appropriate bit of the

P3 register. In terms of hardware, this port is similar to P0, with the difference that its pins have a pull-up resistor built-in.

\_\_\_\_\_

### 5. Explain the timers modes of 8051 (Nov/Dec 2015) (May/June 2017)

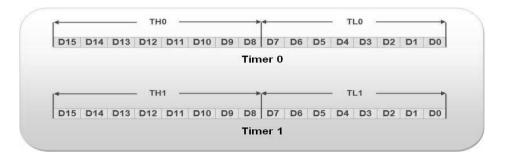

The 8051 has two 16-bit on chip timers that can be used for timing durations or for counting external events. The two timers are shown in the below figure .

#### 8051 Timer Mode Control (TMOD) Special Function Register

This is an 8-bit register which is used by both timers 0 and 1 to set the various timer modes. In this TMOD register, lower 4 bits are set aside for timer0 and the upper 4 bits are set aside for timer1. In each case, the lower 2 bits are used to set the timer mode and upper 2 bits to specify the operation.

| GATE | C/T    | M1 | M0 | GATE | $C/\overline{T}$ | M1   | M0 |

|------|--------|----|----|------|------------------|------|----|

|      | Timer1 |    |    |      | Tir              | ner0 |    |

Fig. TMOD Register

- ▶ Bit 7: Gate bit; when set, timer only runs while \INT high. (T0)

- Bit 6: Counter/timer select bit; when set timer is an event counter when cleared timer is an interval timer (T0)

- ➢ Bit 5: Mode bit 1 (T0)

- $\blacktriangleright$  Bit 4: Mode bit 0 (T0)

- ▶ Bit 3: Gate bit; when set, timer only runs while \INT high. (T1)

- Bit 2: Counter/timer select bit; when set timer is an event counter when cleared timer is an interval timer (T1)

- Bit 1: Mode bit 1 (T1)

- $\blacktriangleright \quad \text{Bit 0: Mode bit 0 (T1)}$

## Timer modes

| M1 | M0 | Mode   | Description                     |

|----|----|--------|---------------------------------|

| 0  | 0  | Mode 0 | 13-bit mode (not commonly used) |

| 0  | 1  | Mode 1 | 16-bit timer mode               |

| 1  | 0  | Mode 2 | 8-bit auto-reload mode          |

| 1  | 1  | Mode 3 | Split timer mode                |

**Mode 1-** It is a 16-bit timer; therefore it allows values from 0000 to FFFFH to be loaded into the timer's registers TL and TH. After TH and TL are loaded with a 16-bit initial value, the timer must be started. We can do it by "SETB TR0" for timer 0 and "SETB TR1" for timer 1. After the timer is started. It starts count up until it reaches its limit of FFFFH. When it rolls over from FFFF to 0000H, it sets high a flag bit called TF (timer flag). This timer flag can be monitored. When this timer flag is raised, one option would be stop the timer with the instructions "CLR TR0" or CLR TR1 for timer 0 and timer 1 respectively. Again, it must be noted that each timer flag TF0 for timer 0 and TF1 for timer1. After the timer reaches its limit and rolls over, in order to repeat the process the registers TH and TL must be reloaded with the original value and TF must be reset to 0.

**Mode0-** Mode 0 is exactly same like mode 1 except that it is a 13-bit timer instead of 16bit. The 13-bit counter can hold values between 0000 to 1FFFH in TH-TL. Therefore, when the timer reaches its maximum of 1FFH, it rolls over to 0000, and TF is raised.

**Mode 2-** It is an 8 bit timer that allows only values of 00 to FFH to be loaded into the timer's register TH. After TH is loaded with 8 bit value, the 8051 gives a copy of it to TL. Then the timer must be started. It is done by the instruction "SETB TR0" for timer 0 and "SETB TR1" for timer1. This is like mode 1. After timer is started, it starts to count up by incrementing the TL register. It counts up until it reaches its limit of FFH. When it rolls over from FFH to 00. It sets high the TF (timer flag). If we are using timer 0, TF0 goes high; if using TF1 then TF1 is raised. When Tl register rolls from FFH to 00 and TF is set to 1, TL is reloaded automatically with the original value kept by the TH register. To repeat the process, we must simply clear TF and let it go without any need by the programmer to reload the original value. This makes mode 2 auto reload, in contrast in mode 1 in which programmer has to reload TH and TL.

**Mode3-** Mode 3 is also known as a split timer mode. Timer 0 and 1 may be programmed to be in mode 0, 1 and 2 independently of similar mode for other timer. This is not true for mode 3; timers do not operate independently if mode 3 is chosen for timer 0. Placing timer 1 in mode 3 causes it to stop counting; the control bit TR1 and the timer 1 flag TF1 are then used by timer0.

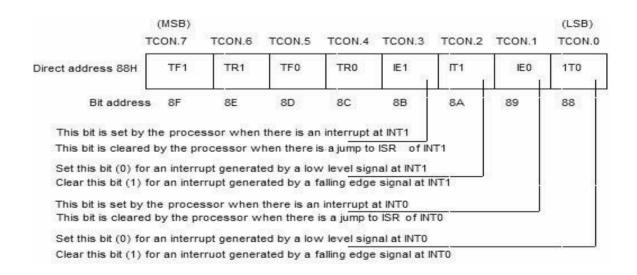

## TCON register-

Bits and symbol and functions of every bits of TCON are as follows:

BIT Symbol

Functions

| 7<br>Cleared | TF1 | Timer1 over flow flag. Set when timer rolls from all 1s to 0.       |

|--------------|-----|---------------------------------------------------------------------|

|              |     | When the processor vectors to execute interrupt service routine     |

|              |     | Located at program address 001Bh.                                   |

| 6            | TR1 | Timer 1 run control bit. Set to 1 by programmer to enable timer to  |

|              |     | count; Cleared to 0 by program to halt timer.                       |

| 5            | TF0 | Timer 0 over flow flag. Same as TF1.                                |

| 4            | TR0 | Timer 0 run control bit. Same as TR1.                               |

| 3            | IE1 | External interrupt 1 Edge flag. Not related to timer operations.    |

| 2            | IT1 | External interrupt1 signal type control bit. Set to 1 by program to |

| signal.      |     | Enable external interrupt 1 to be triggered by a falling edge       |

| 1            | IE0 | External interrupt 0 Edge flag. Not related to timer operations.    |

| 0            | IT0 | External interrupt 0 signal type control bit. Same as IT0.          |

|              |     |                                                                     |

## 6. Explain the interrupt structure of 8051 microcontroller Explain how interrupts are Prioritized (May/june 2016, Dec 2016).

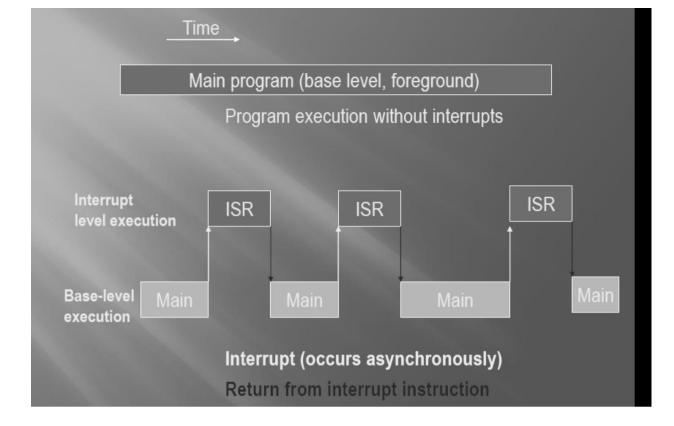

- ➤ An interrupt is the occurrence of a condition--an event -- that cause a temporary suspension of a program while the event is serviced by another program (Interrupt Service Routine ISR or Interrupt Handler).

- Interrupt-Driven System-- gives the illusion of doing many things simultaneously, quick response to events, suitable for real-time control application.

- > The entire interrupt handling process is shown in the below figure.

#### **8051 INTERRUPT ORGANIZATION**

5 interrupt sources: 2 external, 2 timer, a serial port. The interrupts and their vector addresses are listed in the below table

| Interrupt Number | Interrupt Description | Address |

|------------------|-----------------------|---------|

| 0                | EXTERNAL INT 0        | 0003h   |

| 1                | TIMER/COUNTER 0       | 000Bh   |

| 2                | EXTERNAL INT 1        | 0013h   |

| 3                | TIMER/COUNTER 1       | 001Bh   |

| 4                | SERIAL PORT           | 0023h   |

# <u>ENABLING AND DISABLING INTERRUPTS – Using IE Register (INTERRUPT ENABLE REGISTER -A8H)</u>

This register is responsible for enabling and disabling the interrupt. It is a bit addressable register in which EA must be set to one for enabling interrupts. The corresponding bit in this register enables particular interrupt like timer, external and serial inputs. In the below IE register, bit corresponding to 1 activates the interrupt and 0 disables the interrupt.

|     |      | EA    | 7                                                 | -            | ES              | EII                          | EXI | E10 | EX0            |               |

|-----|------|-------|---------------------------------------------------|--------------|-----------------|------------------------------|-----|-----|----------------|---------------|

| EA  | IE.7 |       |                                                   | 120010 121   | 5 1949 - Marine | interrupt w<br>setting or cl |     |     | f EA = 1, into | errupt source |

| -   | IE.6 | Not i | mplement                                          | ed, reserved | l for future    | e use*.                      |     |     |                |               |

| -   | IE.5 | Not i | Not implemented, reserved for future use*.        |              |                 |                              |     |     |                |               |

| ES  | IE.4 | Enab  | Enable or disable the Serial port interrupt.      |              |                 |                              |     |     |                |               |

| ET1 | IE.3 | Enab  | Enable or disable the Timer 1 overflow interrupt. |              |                 |                              |     |     |                |               |

| EX1 | IE.2 | Enab  | Enable or disable External interrupt 1.           |              |                 |                              |     |     |                |               |

| ET0 | IE.1 | Enab  | Enable or disable the Timer 0 overflow interrupt. |              |                 |                              |     |     |                |               |

| EX0 | IE.0 | Enab  | le or disat                                       | le External  | Interrupt       | 0.                           |     |     |                |               |

120

and the second second

1371

TITIO

100 B

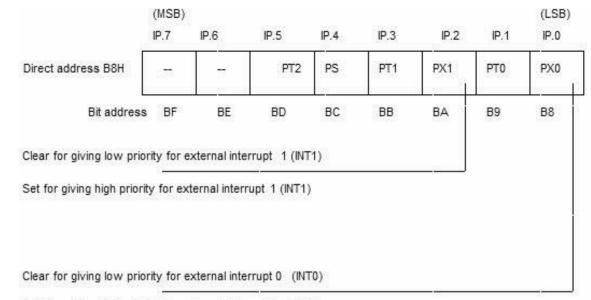

## **PRIORITY OF INTERRUPTS**

The priority levels of the interrupts is changed by setting or clearing the corresponding bit in the Interrupt priority (IP) register as shown in the figure. This allows the low priority interrupt to interrupt the high-priority interrupt, but prohibits the interruption by another low priority interrupt. Similarly, the high-priority interrupt cannot be interrupted. If these interrupt priorities are not programmed, the microcontroller executes in predefined manner and its order is

> INT0 (Highest) TF0 INT1 TF1 SERIAL PORT (lowest)

#### **INTERRUPT PRIORITY (IP) REGISTER**

Set for giving high priority for external interrupt 0 (INT0)

#### **TCON REGISTER**

In addition to the above two registers, the TCON register specifies the type of external interrupt to the 8051 microcontroller, as shown in the figure. The two external interrupts, whether edge or level triggered, specify by this register by a set, or cleared by appropriate bits in it. And, it is also a bit addressable register. The TCON register is shown in the figure.

7. Compare the programming concepts of 8085 with 8051.

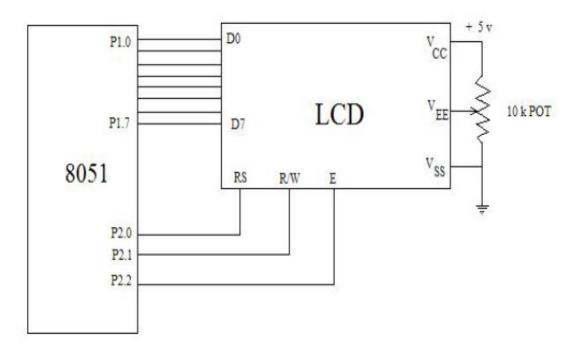

| S.NO | Assembly language instructions of 8085                                                                                                                                                                                                                                                                                                                                                                                                                                            | Assembly language instructions of 8051                                                                                                                                                                                                                                                                                                                                                                                                                                                |